FPGA-VGA

目录

前言

一、VGA是什么?

二、物理接口

三、VGA显示原理

四、VGA时序标准

五、VGA显示参数

六、模块设计

七、波形图设计

八、彩条波形数据

前言

VGA的FPGA驱动

一、VGA是什么?

VGA(Video Graphics Array)是IBM于1987年推出的显示标准,涵盖硬件接口、分辨率和图形处理规范。常见的视频传输接口有三种:VGA 接口、DVI 接口和HDMI 接口,目前的显示设备都配有这三种视频传输接口。

三类视频接口的发展历程为VGA→DVI→HDMI。

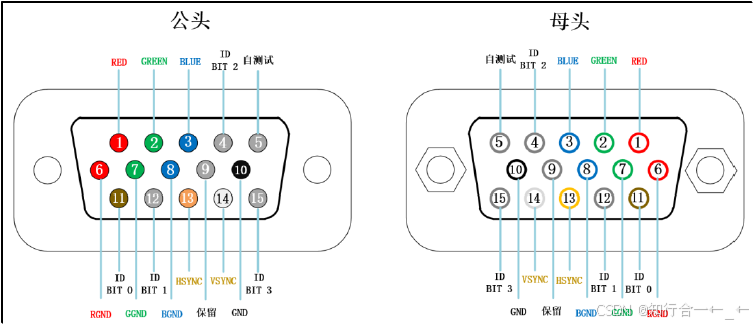

二、物理接口

接口解释:

1. 核心信号传输(RGB三原色)

-

Pin 1(Red):传输红色分量的模拟信号。

-

Pin 2(Green):传输绿色分量的模拟信号。

-

Pin 3(Blue):传输蓝色分量的模拟信号。

作用:RGB三原色信号组合形成完整的图像色彩,信号强度决定像素亮度。

2. 同步信号(Sync)

-

Pin 13(Horizontal Sync):传输水平同步信号,控制显示器横向扫描的时序。

-

Pin 14(Vertical Sync):传输垂直同步信号,控制显示器纵向刷新的时序。

作用:同步信号确保显示器与显卡输出的图像帧率匹配,避免画面撕裂或偏移。

3. 地线(Ground)

-

Pin 5(Ground):RGB信号的公共地线。

-

Pin 6(Red Ground):红色信号专用地线。

-

Pin 7(Green Ground):绿色信号专用地线。

-

Pin 8(Blue Ground):蓝色信号专用地线。

-

Pin 10(Sync Ground):同步信号的公共地线。

作用:地线用于消除信号干扰,稳定传输质量。不同信号单独接地可减少串扰。

4. 其他功能针脚

-

Pin 4(ID2 / Reserved):早期用于显示器识别(ID Bit 2),现多为保留未用。

-

Pin 9(+5V DC):提供5V电源,早期用于某些显示器检测或DDC芯片供电。

-

Pin 11(ID0 / Reserved):显示器识别位(ID Bit 0),现通常未使用。

-

Pin 12(ID1 / SDA):部分设备用于DDC(Display Data Channel)通信的SDA数据线。

-

Pin 15(ID3 / SCL):部分设备用于DDC通信的SCL时钟线。

作用:DDC功能允许显示器自动向显卡报告分辨率等信息(类似即插即用)。

关键接口是三个基色接口,以及行同步接口和场同步接口。

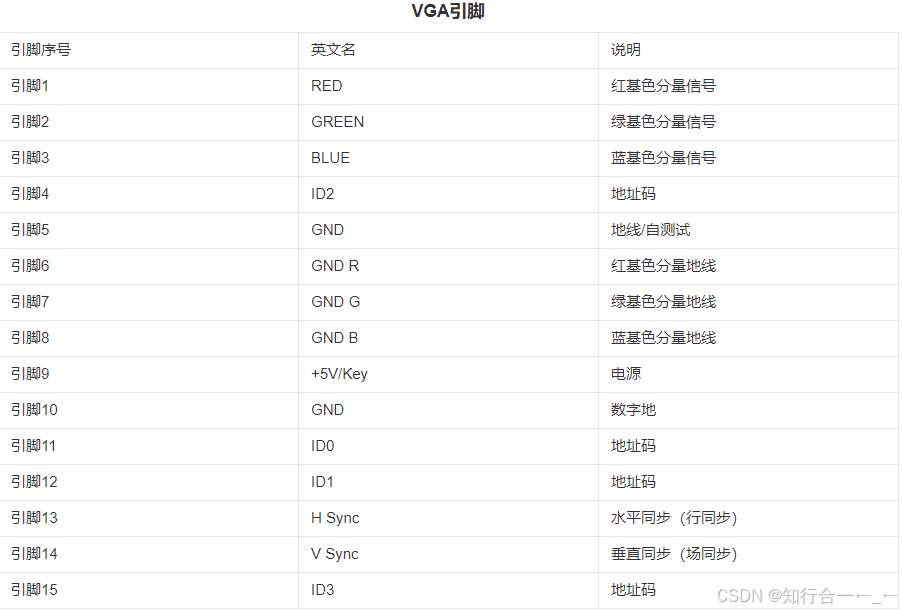

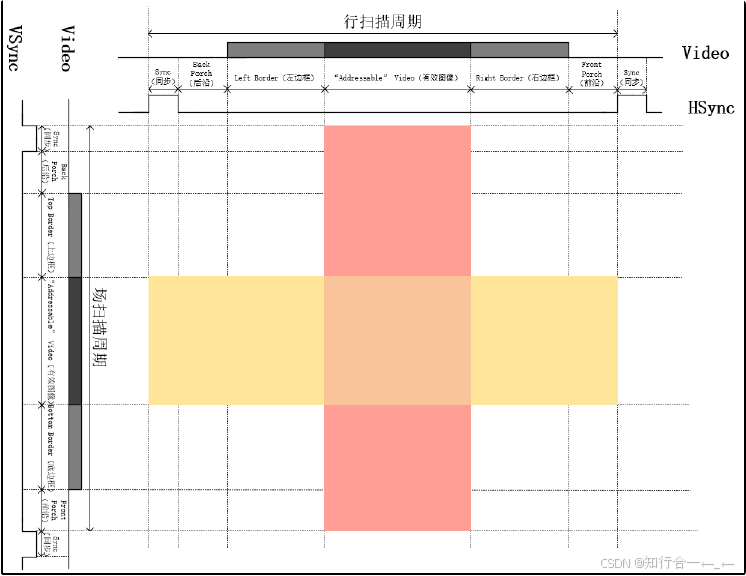

三、VGA显示原理

VGA 显示器显示图像,并不是直接让图像在显示器上显示出来,而是采用扫描的方

式,将构成图像的像素点,在行同步信号和场同步信号的同步下,按照从上到下、由左到

右的顺序扫描到显示屏上。

一行一行的扫描。

为什么我的扫描的这么慢,怎么改变帧率,提高或者降低帧率。

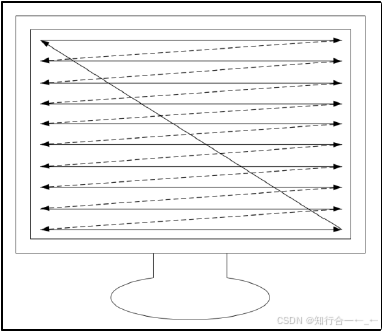

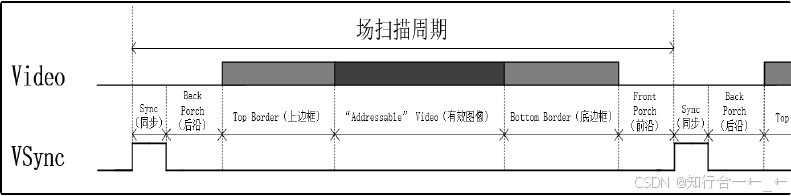

四、VGA时序标准

上面的时序也只是一种,也有其它的时序,比如反过来的。

代码如下(示例):

每个时钟周期传输一个像素点,深色部分有多个时钟周期,每个时钟周期对应一个像素点,上面是一个像素点的时钟周期,这个时钟周期也叫像素时钟周期。

每次扫描一帧图像,相交部分是显示区域,是一帧图像。

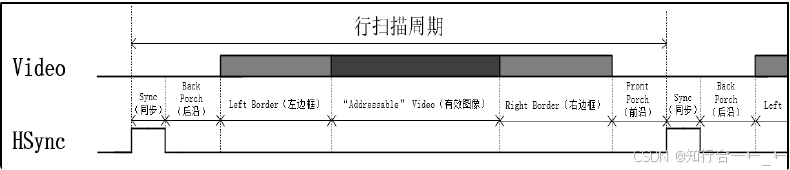

五、VGA显示参数

640x480@60的含义是,显示屏是640列,480行,60帧的速率。这60帧我没看到和感受到啊。

640x480约30_0000个像素点。

行扫描周期x场扫描周期x帧率=像素时钟(Mhz),这是行场同步的时钟频率。

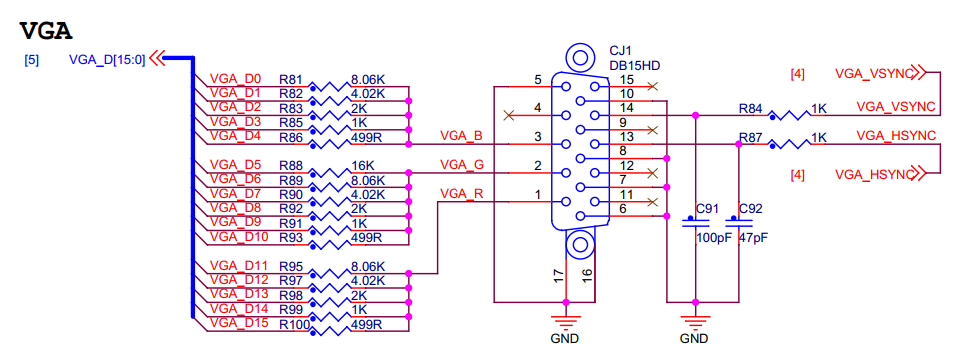

由于VGA的输入是模拟信号,将数字信号转换为模拟信号,可以采用权电阻网络或者是专用的转换芯片。

这是RGB565的格式,用电压来表示颜色的深度,这三路模拟信号的电压范围为0V ~ 0.714V,0V 代表无色,0.714V 代表满色,电压高低由输入的数字信号决定。输入的R、G、B 数字信号不同,输出的三原色红、绿、蓝电压不同,颜色深浅不同,三原色相结合可以产生多种颜色。

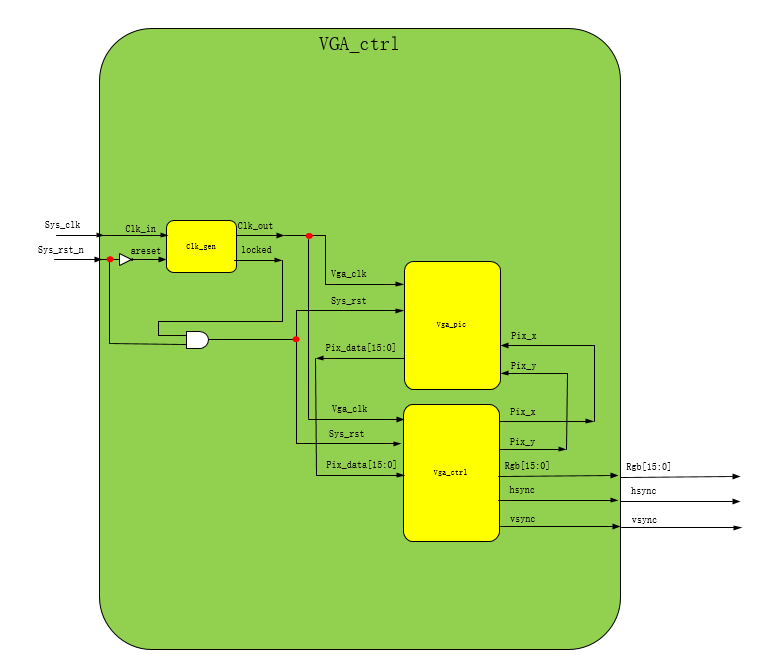

六、模块设计

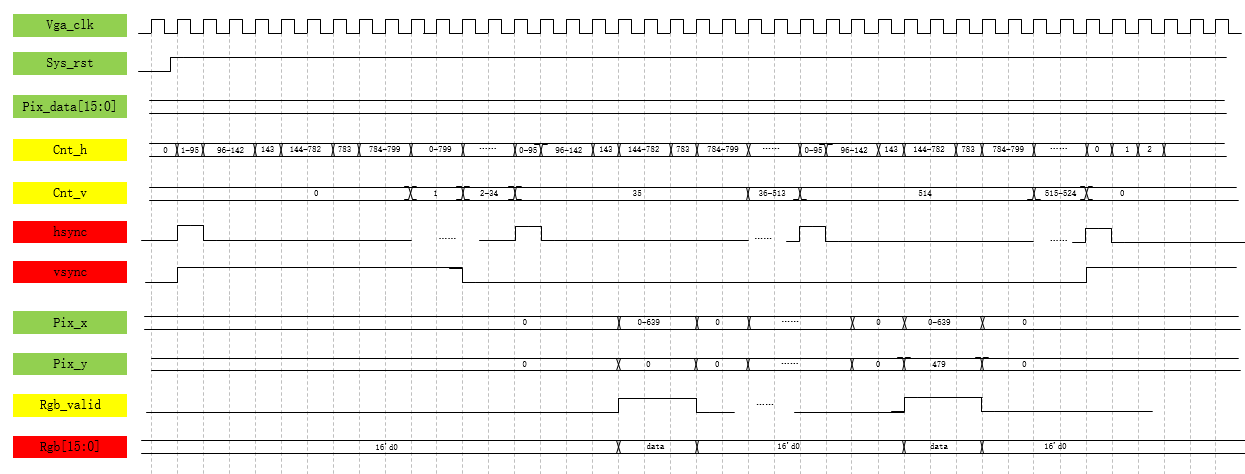

七、波形图设计

一个行扫描周期是扫描一行,扫描完一行,列计数器计数一个,图像是在对应的行扫描周期和列扫描周期的对应时间来判断的。

图像有效信号范围,计数从0开始

行计数器范围(96+40+8-1=143,96+40+8+640-1=783)

场计数器范围(2+25+8-1=34,2+25+8+480-1=514)

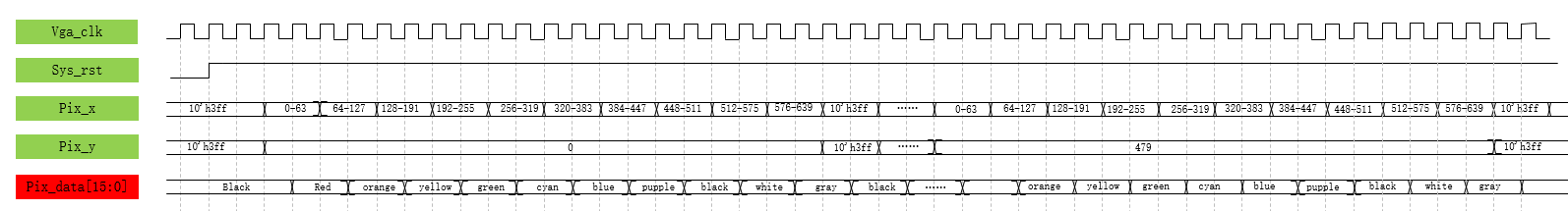

八、彩条波形数据

640是列的个数

480是行的个数

对行进行10等分。

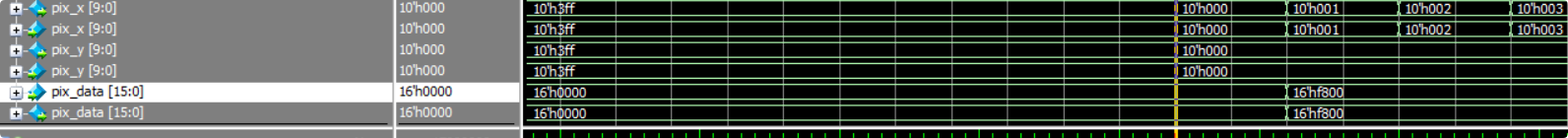

在有些时候对于数据的初始化可以不用0,改用其他的不常见或者不可能数值。比如数据变化范围是0-100,位宽是8位,可以初始化为8'hff,防止在数据误操作,比如在0到10要进行一个操作,那么初始化为0就会在开始时发生误操作,但是初始化为8‘hff,就不会发生误操作。

有时数据需要对齐边沿。

数据滞后坐标一个时钟周期,在vga_ctrl里产生对应的坐标,然后图像生成模块在一个时钟周期内输出对应的图像数据。图像数据经过组合逻辑立刻经过vga_ctrl输出图像。

数据滞后位置的波形图。