闩锁效应(latch up)

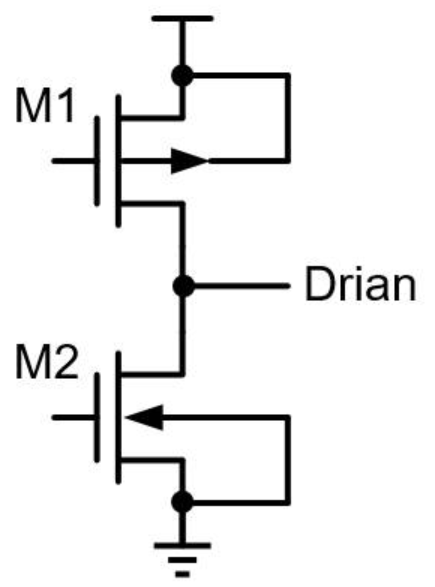

下图为cmos工艺下的电路图:

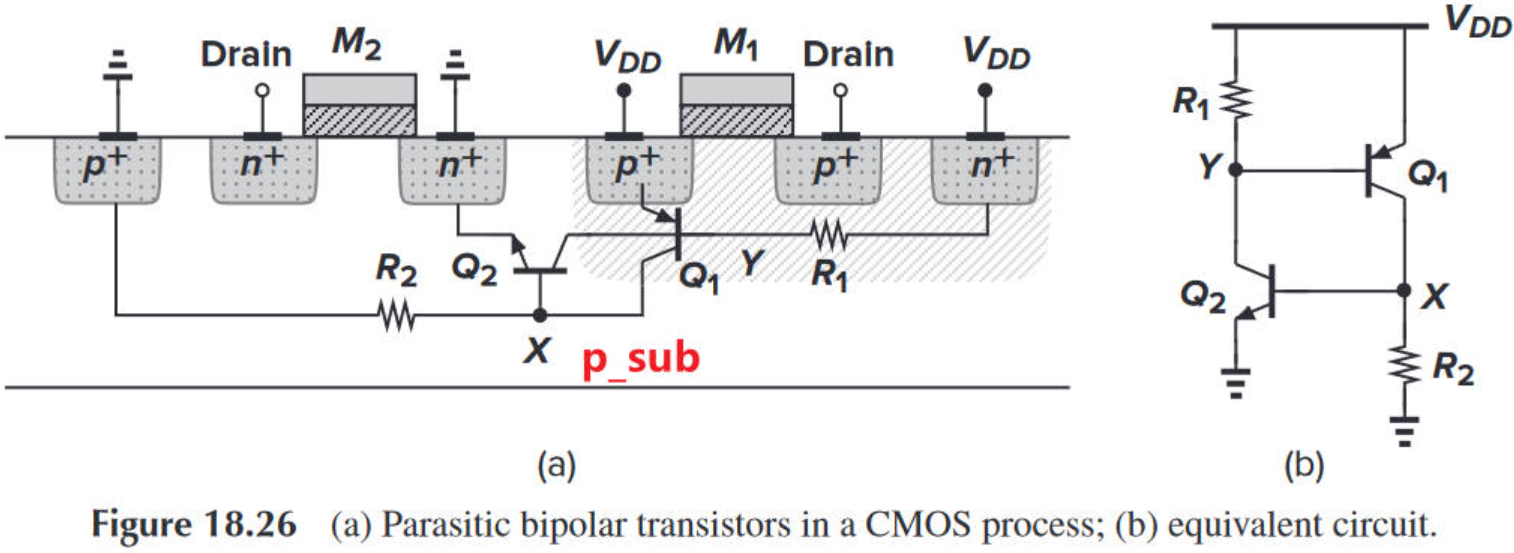

拉扎维书上给出了对应的cmos工艺图:

依据上图可以解释latch up产生的原因和后果:

图(a)展示了PMOS提供一个寄生pnp Q1,NMOS提供一个寄生npn Q2,并且每个bipolar的B端一定接在另外一个C端,同时N-WELL和psub具有一定的寄生电阻分别为R1和R2。

如图(b)所示的等效电路,当X点有电流注入时,Vx上升,然后Ic2增大,从而Y点电压减小,使得|Ic1|的增大(pnp的C端电流与npn的C端电流反向,故增加一个绝对值符号),导致X点电压进一步增大。

如果这一环路增益大于等于1,则两个晶体管完全导通,从vdd抽取很大电流,甚至烧坏器件。

避免latch up的方案:

根据版图规则,选择适当的杂质浓度和分布以减小寄生bipolar的电流增益系数Bata,以及降低衬底接触孔和n阱接触孔的间隔,从而降低接触电阻。

具体操作:增加guard ring