MCU开发学习记录10 - 高级定时器学习与实践(HAL库)—PWM互补输出、死区控制、刹车控制 - STM32CubeMX

本文将介绍高级定时器的概念(只讲解高级定时器特有功能)、相关函数以及STM32CubeMX生成定时器的配置函数以及对生成定时器的配置函数进行分析(包括结构体配置、相关寄存器配置)。针对于高级定时器实践:实现输出PWM互补波同时添加死区控制和刹车功能。

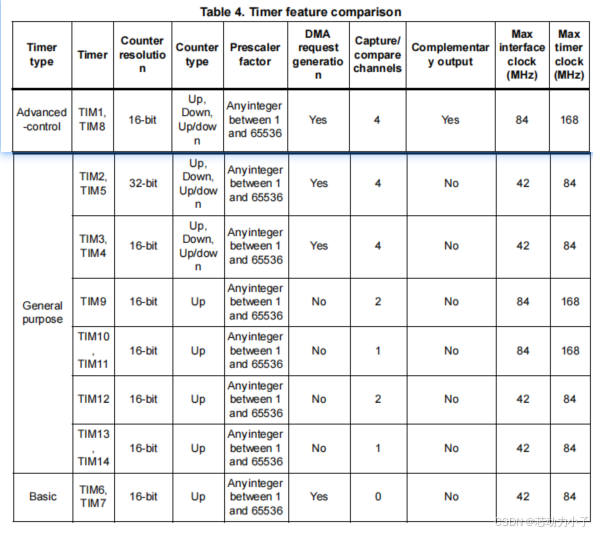

0. F4系列定时器分类

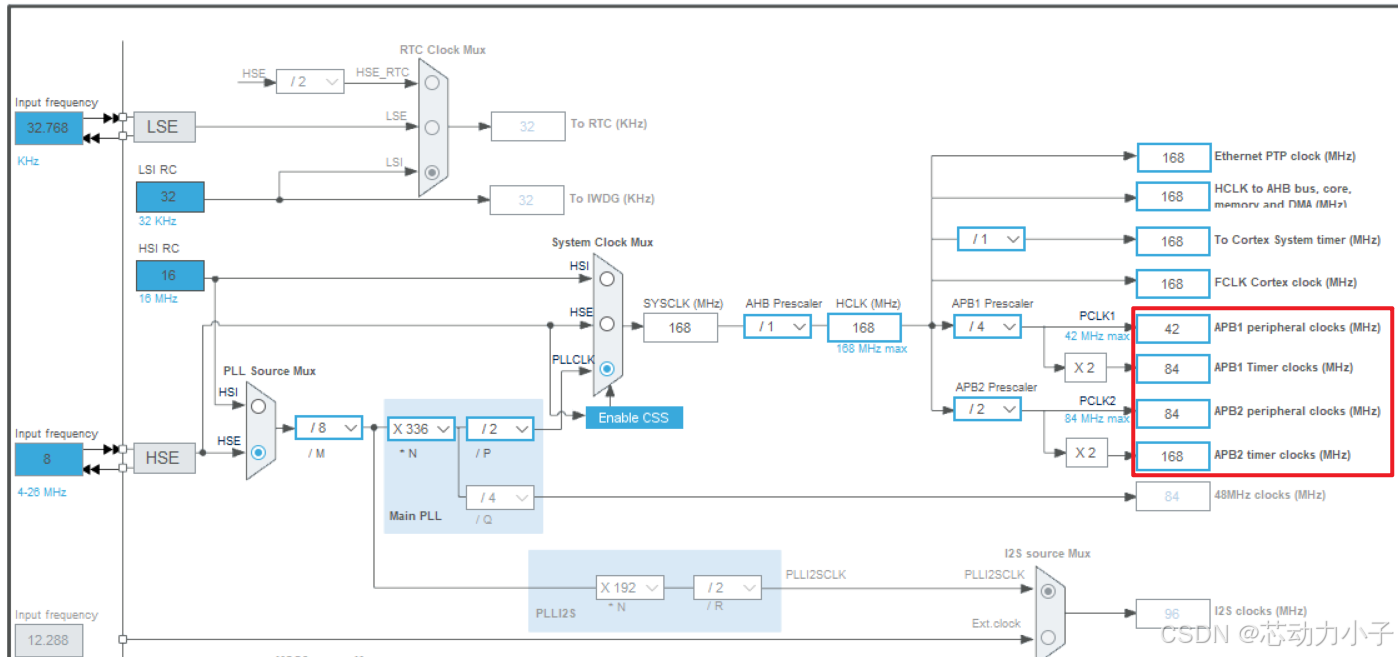

- 最大接口时钟(Max interface clock (MHz))

1. 定时器与系统内核(如MCU)之间的通信接口(如APB总线)支持的最高时钟频率。

2. 它决定了定时器寄存器配置和状态读取的速度上限。例如,如果接口时钟为84 MHz,则对定时器寄存器的读写操作需基于该频率进行,不能超过此速率。 - 最大定时器时钟(Max timer clock (MHz))

1. 定时器内部计数器(Counter)实际运行时的最高时钟频率。

2. 它决定了定时器的计数速度,直接影响定时器的计时精度和输出信号的频率上限。例如,168 MHz的定时器时钟意味着计数器每秒最多递增168,000,000次。

1. 什么是高级定时器?

1.1 高级定时器概念

1.1.1 高级定时器功能

1. 计数器

- 16位递增/递减/自动重载计数器

- 16位可编程预分频器

- 分频系数范围:1 ~ 65536

- 支持运行时动态修改分频参数

2. 通道功能(最多4个独立通道,支持):

- 输入捕获(测量信号时间参数)

- 输出比较(生成特定时序信号)

- PWM生成(边沿对齐/中心对齐模式)

- 单脉冲模式(触发后输出单次脉冲)

3. 互补输出与刹车保护

- 可编程死区互补输出(防止功率器件短路)

- 断路输入功能(紧急复位输出信号

4. 同步与互联

- 支持外部信号控制定时器

- 多定时器互连同步(协同复杂时序任务)

5. 中断与事件管理

- 重复计数器(延迟寄存器更新至指定周期数)

- 中断/DMA触发事件:

- 计数器溢出/下溢/初始化

- 触发事件(启动/停止/复位)

- 输入捕获/输出比较/断路信号

6. 传感器接口、外部信号交互

- 兼容增量式编码器(正交编码器)

- 霍尔传感器电路(电机位置检测)

- 外部时钟触发输入(扩展时钟源)

- 逐周期电流管理(电源/电机控制优化)

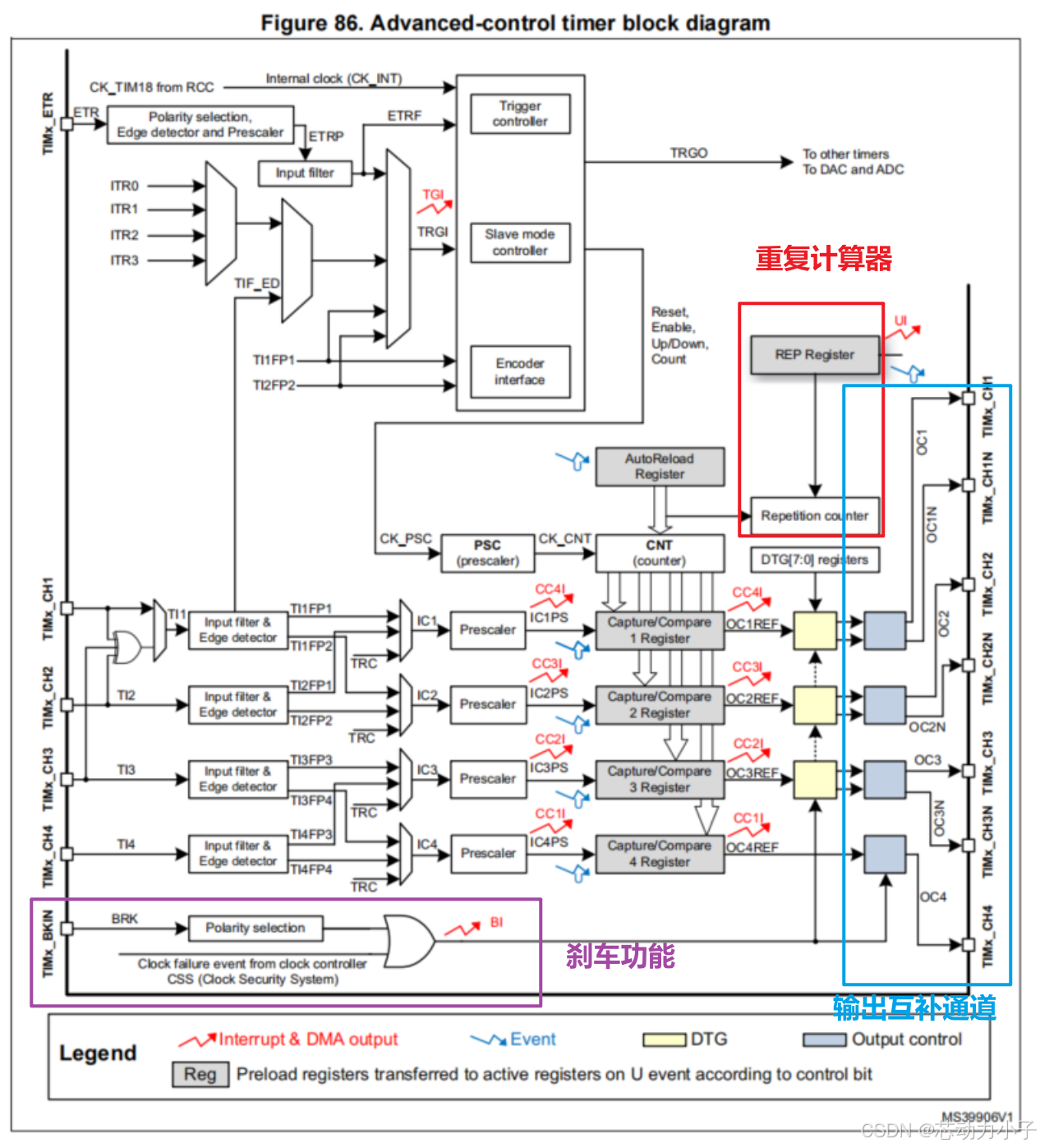

1.1.2 高级定时器框图(仅标出高级定时器多出的功能)

1.2 高级定时器功能(独有的)

1.2.1 重复计数器

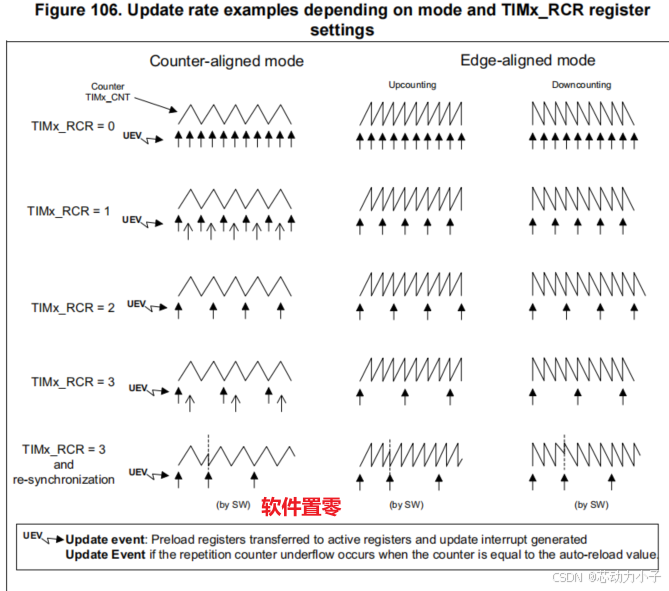

1. 更新事件(UEV)触发条件

- 核心规则:仅当重复计数器(TIMx_RCR)归零时才会生成更新事件(UEV)。

- 作用:UEV触发时,预装载寄存器(如ARR、PSC、CCRx)的数据会转移到影子寄存器(实际生效的寄存器)。

2. 不同计数模式下的UEV生成

边沿对齐模式

- 递增计数:

- UEV在每N+1次上溢时触发(N为TIMx_RCR值)。

- 示例:RCR=3 → 第4次上溢触发UEV。

- 递减计数:

- UEV在每N+1次下溢时触发。

- 示例:RCR=1 → 第2次下溢触发UEV。

中心对齐模式

- 双递减点:每个周期包含上溢和下溢,重复计数器每次递减两次。

- RCR为奇数:UEV触发位置取决于RCR写入时机:

- 启动前写入:在上溢时触发。

- 启动后写入:在下溢时触发。

- 示例:RCR=3 → 第4次上溢或下溢触发UEV(具体取决于写入时机)。

- RCR为奇数:UEV触发位置取决于RCR写入时机:

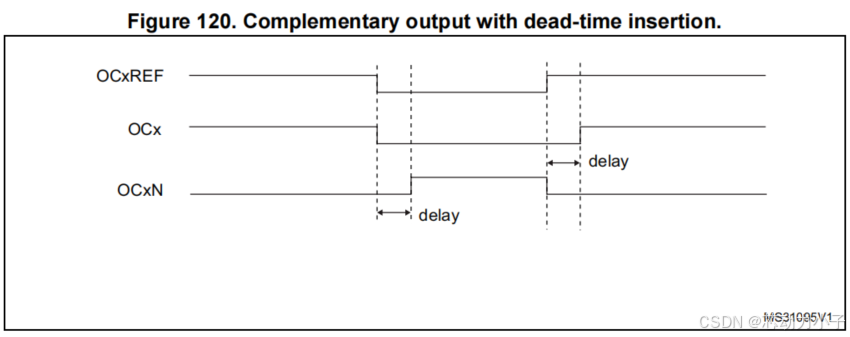

1.2.2 互补输出和死区插入

1. 功能描述

- 高级控制定时器(TIMx)可生成两路互补信号(OCx和OCxN),适用于驱动半桥/全桥电路(如电机控制、电源开关)。

- 死区(Dead Time)指两路信号切换时的空白时段,用于避免功率器件直通短路。

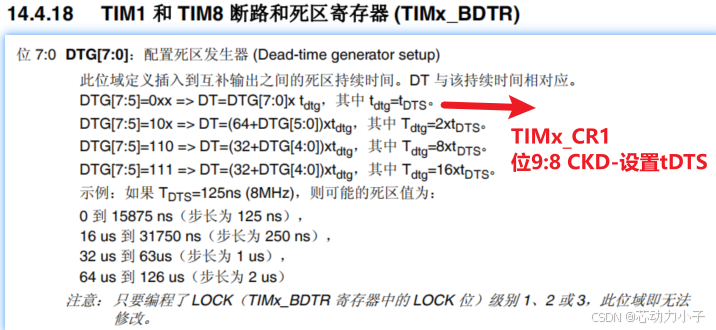

- 每个通道的死区延迟相同,并且可以通过TIMx_BDTR寄存器中的DTG位进行编程。

2. 相关寄存器配置

- 极性控制:

- 通过

TIMx_CCER寄存器的CCxP(OCx极性)和CCxNP(OCxN极性)位选择高/低电平有效。

- 通过

- 激活条件:

- 需要同时满足:

CCxE=1(使能OCx)、CCxNE=1(使能OCxN)、MOE=1(主输出使能,来自TIMx_BDTR寄存器)。

- 需要同时满足:

- 死区生成:

- 通过

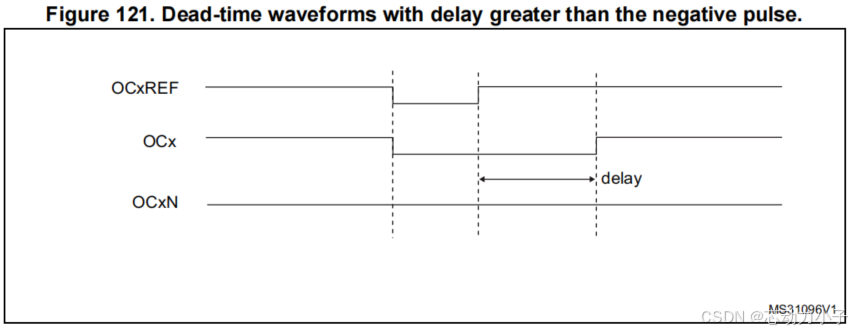

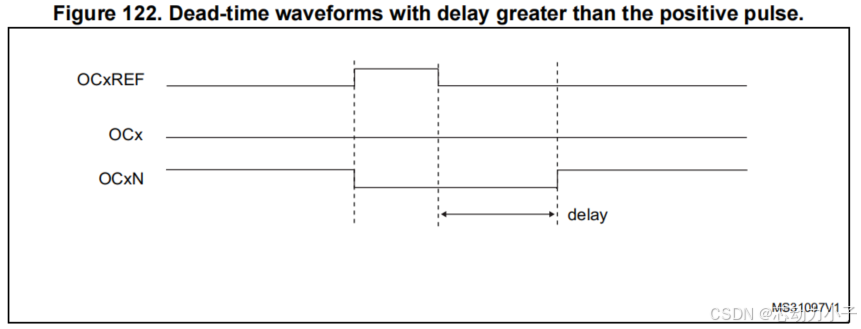

TIMx_BDTR寄存器的DTG[7:0]位编程死区时间。 - 死区波形示例:

- 图105:正常死区插入,OCx/OCxN上升沿延迟。

- 图106:延迟时间超过负脉冲宽度,导致丢失脉冲。

- 图107:延迟时间超过正脉冲宽度,输出保持无效。

- 图105:正常死区插入,OCx/OCxN上升沿延迟。

- 通过

3. 死区事件计算

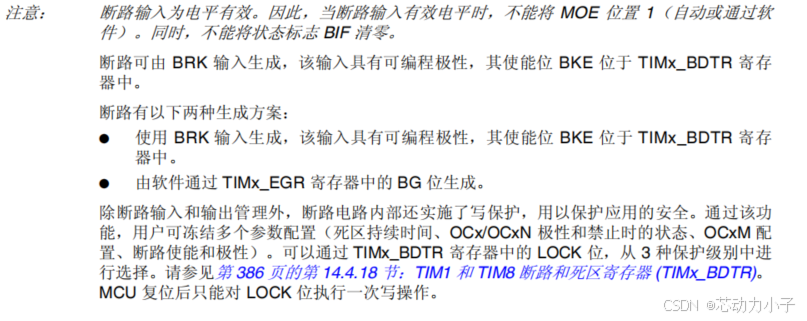

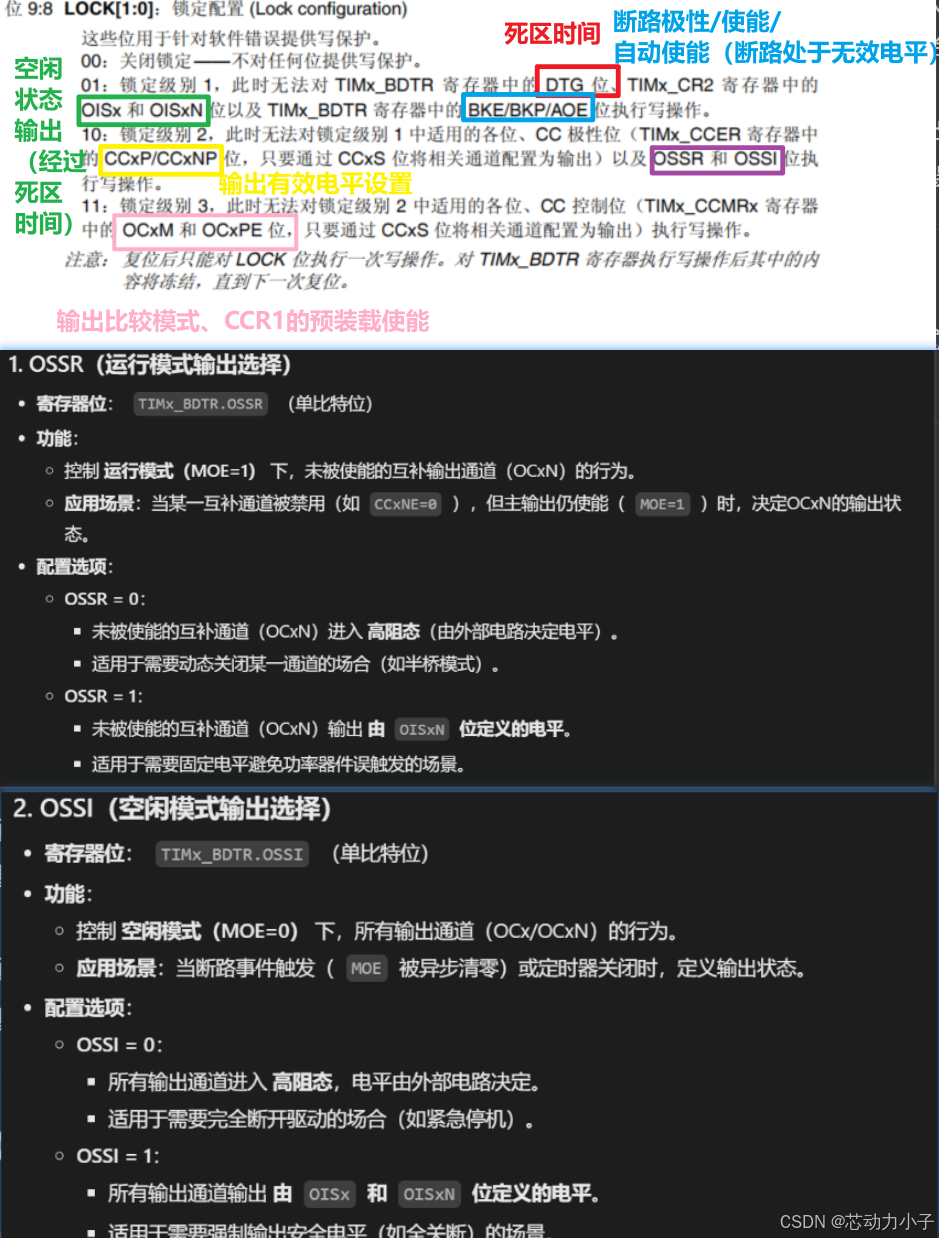

1.2.3 使用断路功能

1. 功能描述

当检测到硬件故障(如过流、过温)时,通过外部断路引脚(BREAK)或时钟安全系统(CSS)触发保护,强制关闭输出。

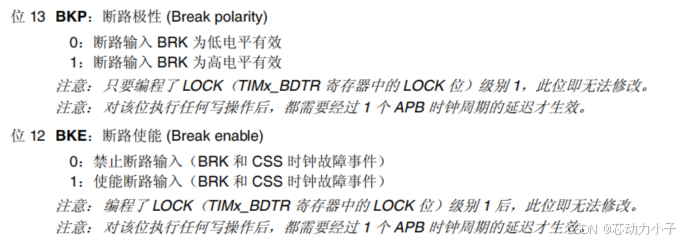

2. 相关寄存器配置

- 触发条件:

- 断路输入引脚有效电平(通过

TIMx_BDTR的BKP位选择高/低触发)。 - 时钟安全系统(CSS)检测时钟失效。

- 断路使能

- 断路输入引脚有效电平(通过

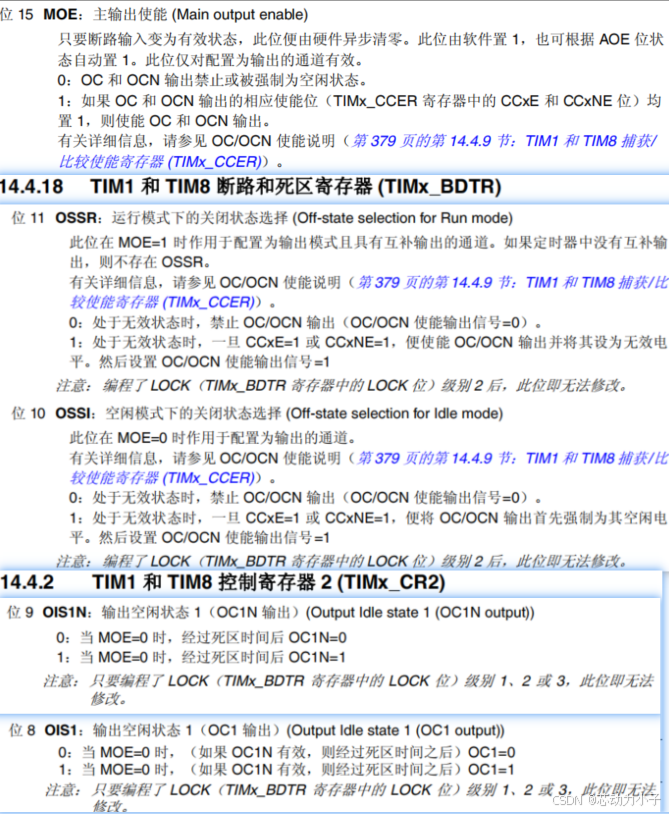

- 响应行为:

MOE位异步清零,输出进入由OSSI(空闲模式选择)和OSSR(运行模式选择)定义的状态:- 无效状态:输出高阻(由外部电路决定电平)。

- 空闲状态:输出固定为

OISx(OCx)或OISxN(OCxN)配置的电平。

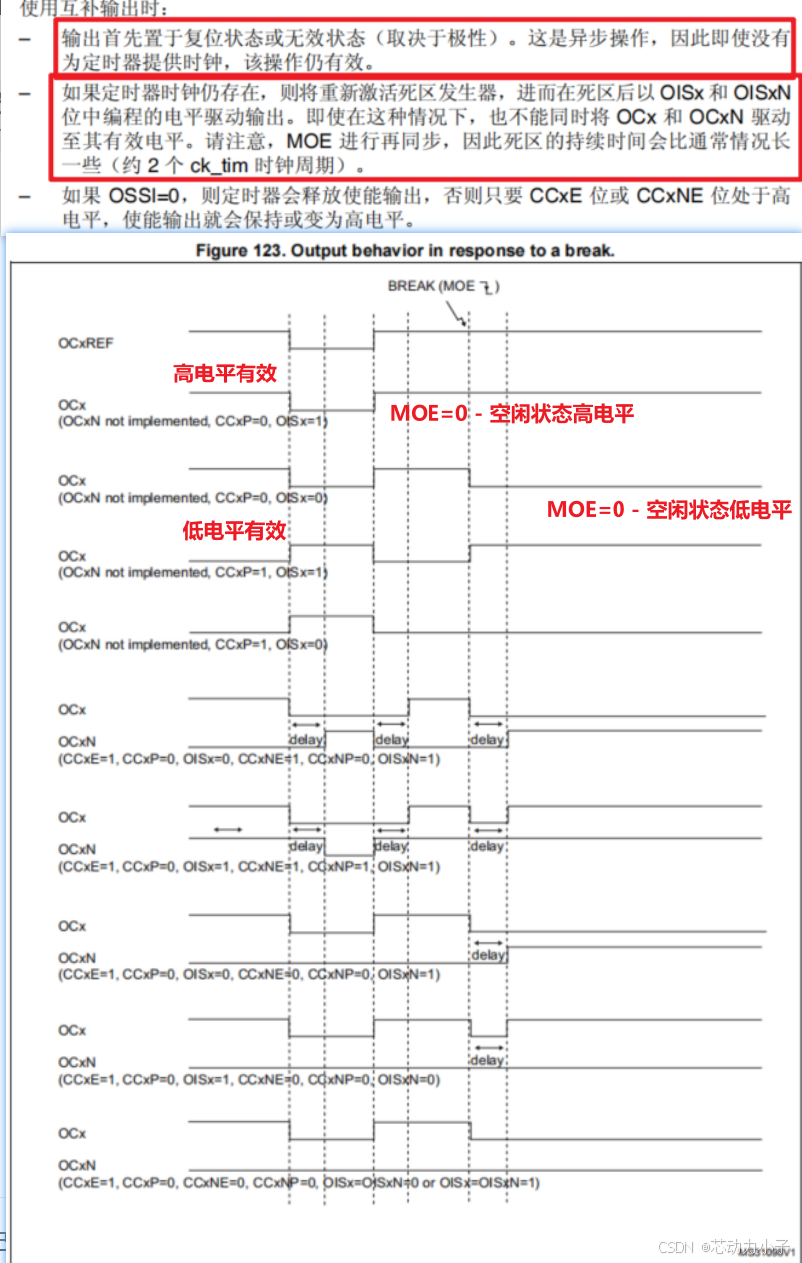

- 示例场景(图108):

- 当

OSSI=0且OSSR=1时,输出释放使能;OSSI=1时保持高电平。 - 断路后需通过软件复位

MOE位恢复输出。

- 当

3. 注意

1.2.4 关于断路和死区寄存器 (TIMx_BDTR).LOCK位

2. 基于HAL库配置高级定时器外设

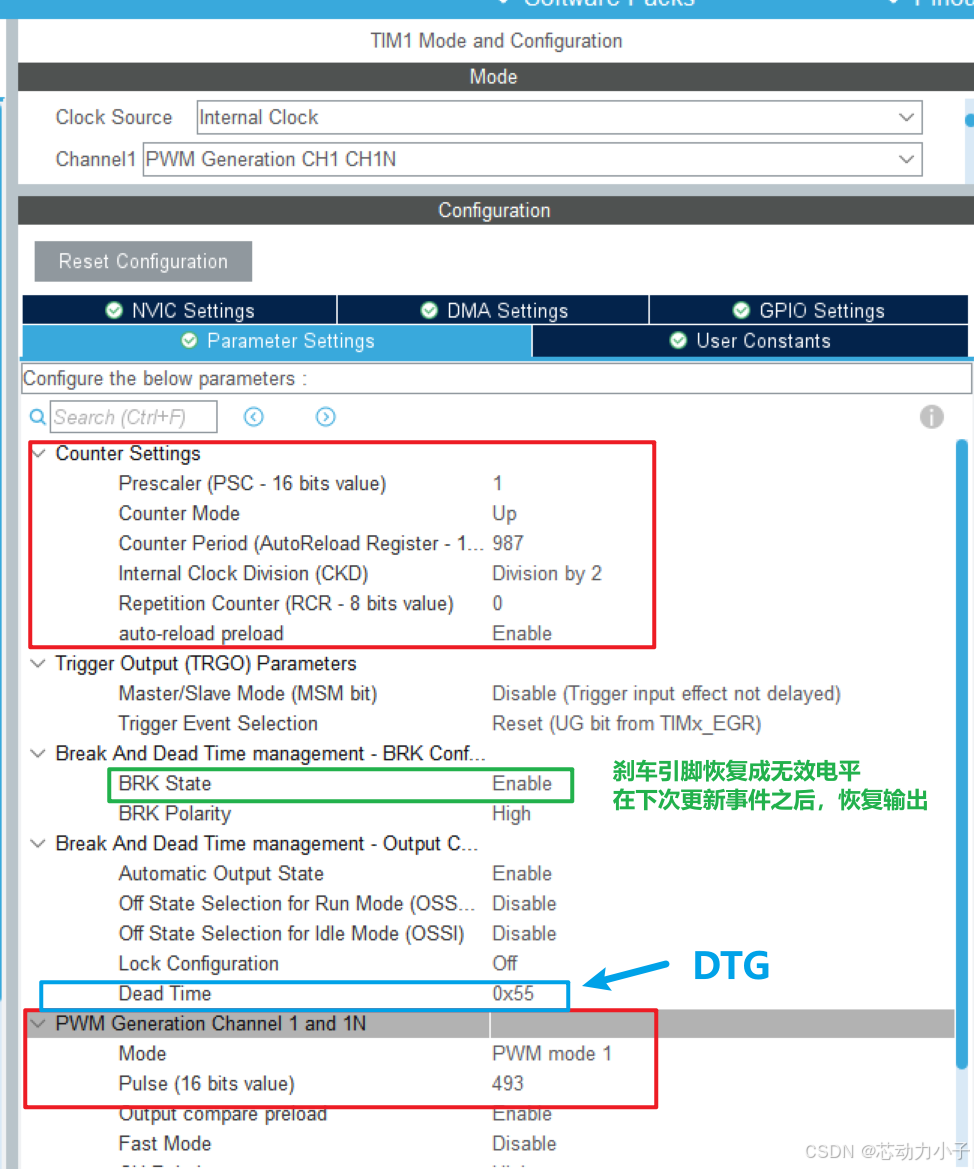

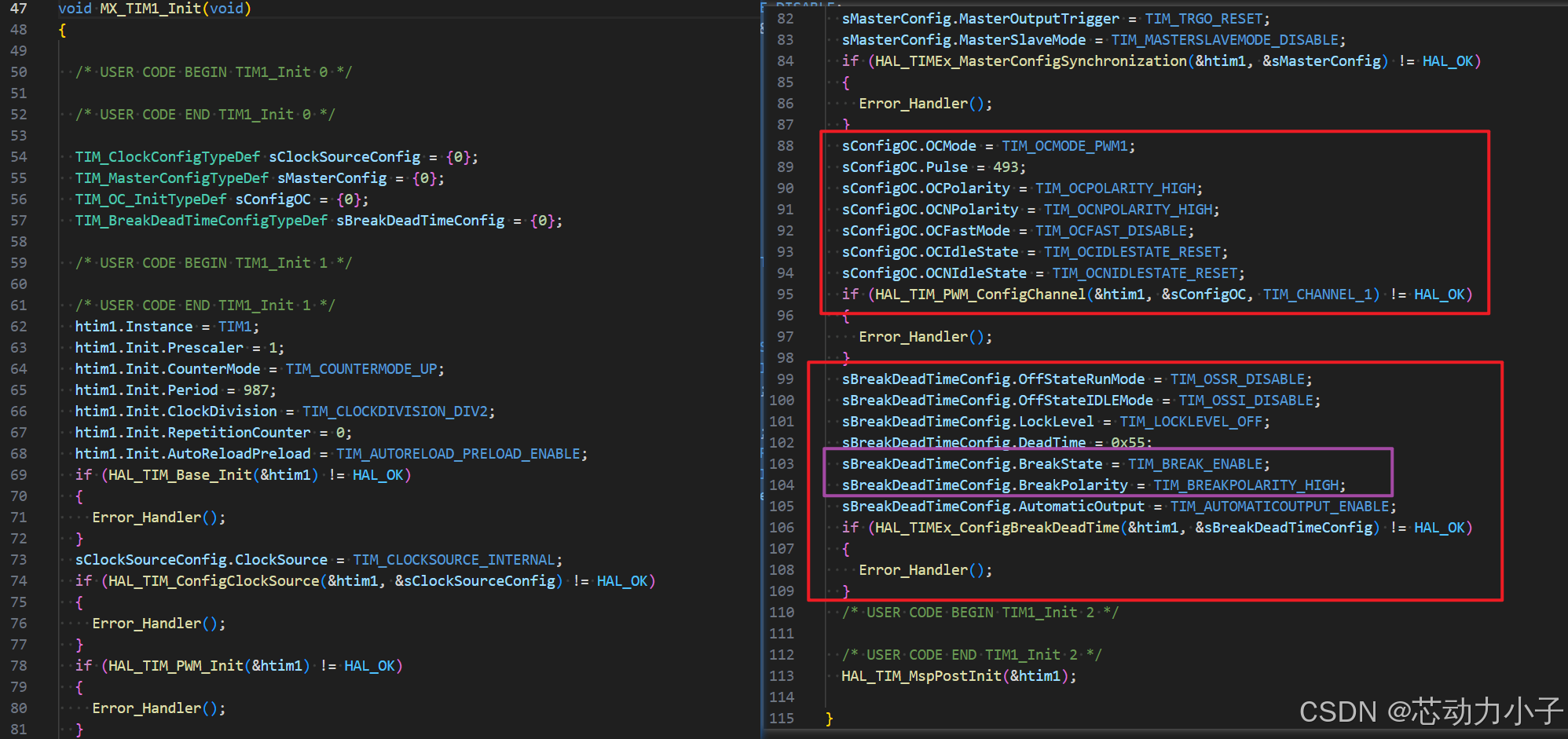

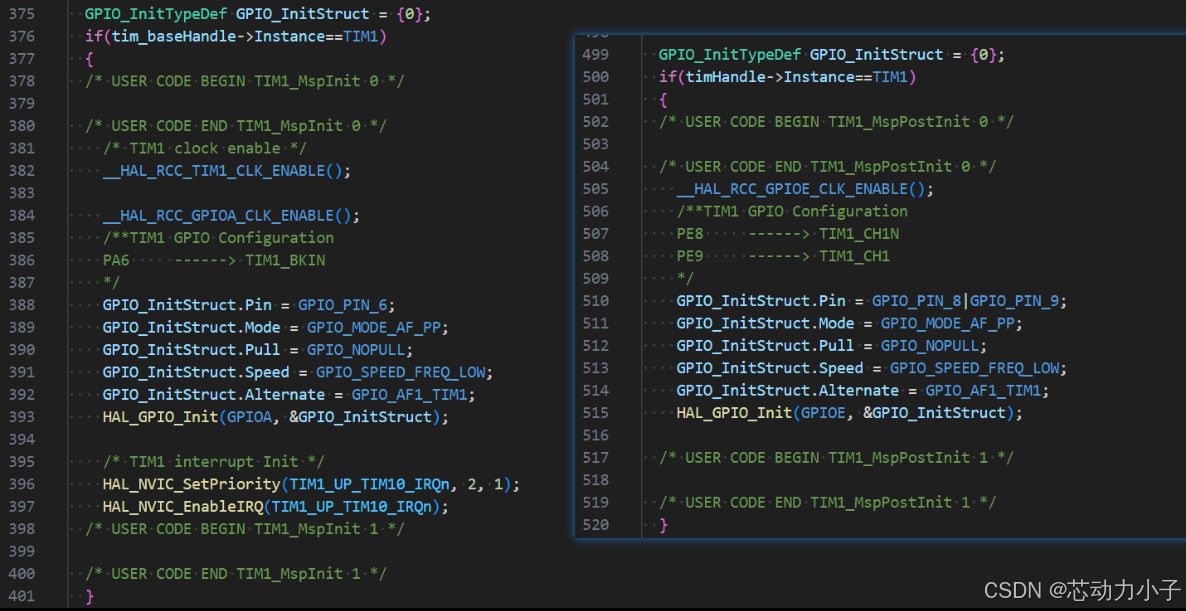

2.1 CubeMX配置高级定时器外设

2.2 高级定时器外设初始化流程

3. 高级定时器实践

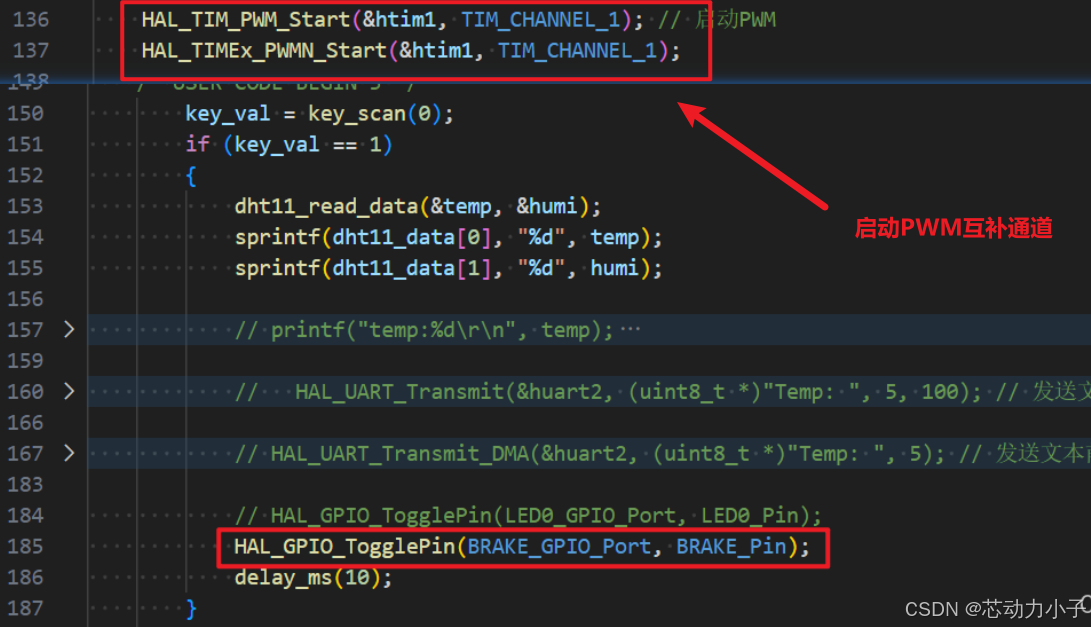

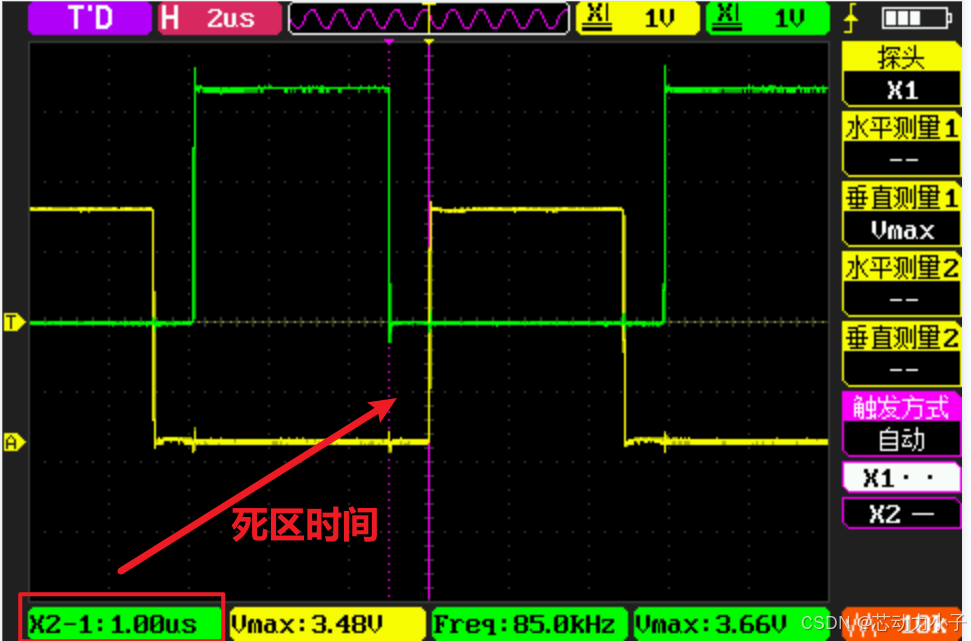

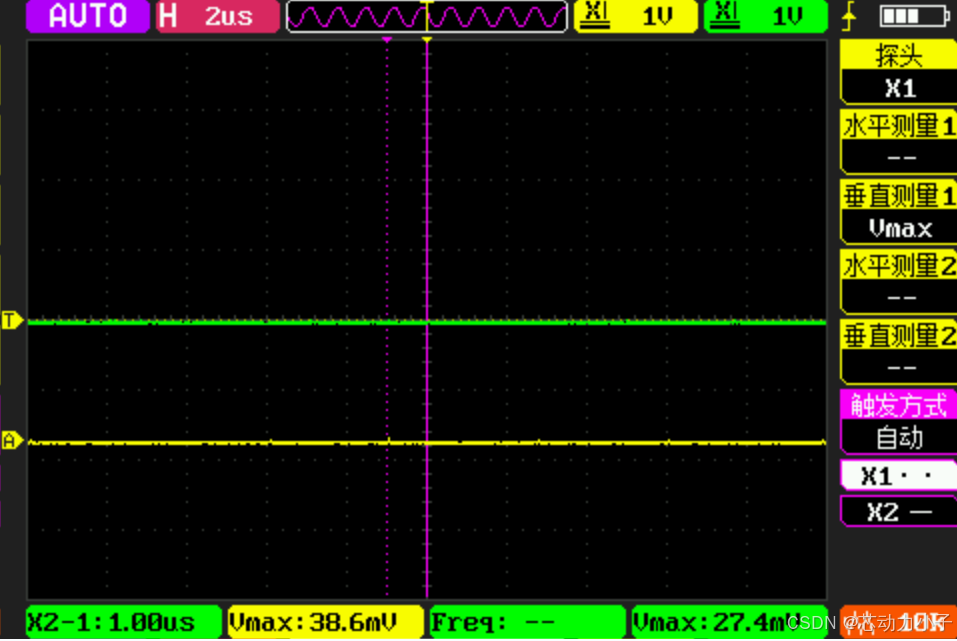

通过KEY0按键控制PF2电平翻转,连接TIM1的刹车引脚(高电平有效),来控制TIM1的ch1/ch1N的互补输出。同时TIM1的ch1/ch1N的互补输出配置了1ms的死区时间。

3.1 用户代码

3.2 实践结果

1. 死区控制

2. 刹车控制(KEY0,再按KEY0恢复输出)

4. 本文的工程文件下载链接

工程Github下载链接:https://github.com/chipdynkid/MCU-DL-STM32

(国内)工程Gitcode下载链接https://gitcode.com/chipdynkid/MCU-DL-STM32