vivado XMP使用

vivado XMP使用

文章目录

- vivado XMP使用

- 前言

- 一、xpm_cdc_async_rst

- 二、XPM_CDC_ARRAY_SINGLE

- 三、XPM_CDC_PULSE

- 四、 XPM_CDC_SINGLE

- 五、 xpm_cdc_sync_rst

- 总结

前言

使用XMP做跨时钟域,方便的是官方认证,好用且不会爆时序问题,懒得写 set flase。

这里不给时序了,参数和使用方法都比较简单,看手册即可

链接如下:

UG974

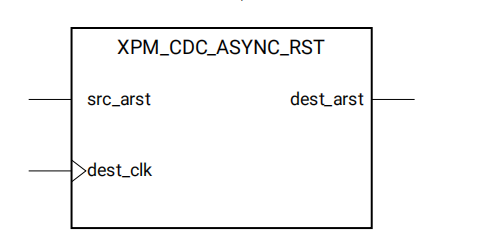

一、xpm_cdc_async_rst

xpm_cdc_async_rst #(.DEST_SYNC_FF(4), // DECIMAL; range: 2-10.INIT_SYNC_FF(0), // DECIMAL; 0=disable simulation init values, 1=enable simulation init values.RST_ACTIVE_HIGH(0) // DECIMAL; 0=active low reset, 1=active high reset)xpm_cdc_async_rst_inst (.dest_arst(dest_arst), // 1-bit output: src_arst asynchronous reset signal synchronized to destination// clock domain. This output is registered. NOTE: Signal asserts asynchronously// but deasserts synchronously to dest_clk. Width of the reset signal is at least// (DEST_SYNC_FF*dest_clk) period..dest_clk(dest_clk), // 1-bit input: Destination clock..src_arst(src_arst) // 1-bit input: Source asynchronous reset signal.);

此宏将异步复位信号同步到目标时钟域。生成的复位输出将保证相对于输入异步断言,但输出的断言始终与目标时钟域同步。您可以定义复位信号的极性和宏断言时的最小输出脉冲宽度。后者通过定义同步器中使用的寄存器级数来控制。注意:最小输入脉冲断言取决于寄存器复位或置位引脚的建立时间和保持时间要求。

- 和同步复位跨时钟域的区别在于断言,异步的是跨时钟之后的复位还是异步断言,但是取消断言是和目标时钟是同步的

- 要保证复位的长度能够足够被目标时钟域采集到,也就是说快采集慢的时钟,复位信号长度一定是两倍以上。否则有问题

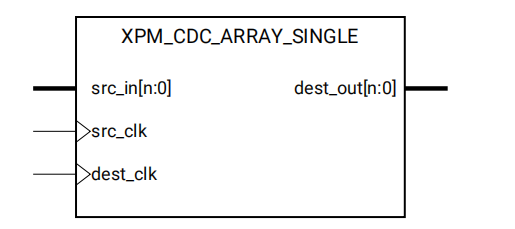

二、XPM_CDC_ARRAY_SINGLE

xpm_cdc_array_single #(.DEST_SYNC_FF(4), // DECIMAL; range: 2-10.INIT_SYNC_FF(0), // DECIMAL; 0=disable simulation init values, 1=enable simulation init values.SIM_ASSERT_CHK(0), // DECIMAL; 0=disable simulation messages, 1=enable simulation messages.SRC_INPUT_REG(1), // DECIMAL; 0=do not register input, 1=register input.WIDTH(2) // DECIMAL; range: 1-1024)xpm_cdc_array_single_inst (.dest_out(dest_out), // WIDTH-bit output: src_in synchronized to the destination clock domain. This// output is registered..dest_clk(dest_clk), // 1-bit input: Clock signal for the destination clock domain..src_clk(src_clk), // 1-bit input: optional; required when SRC_INPUT_REG = 1.src_in(src_in) // WIDTH-bit input: Input single-bit array to be synchronized to destination clock// domain. It is assumed that each bit of the array is unrelated to the others. This// is reflected in the constraints applied to this macro. To transfer a binary value// losslessly across the two clock domains, use the XPM_CDC_GRAY macro instead.);

此宏从源时钟域合成一个单比特信号数组到目标时钟域。为了正常工作,输入数据必须被目标时钟采样两次或更多次。您可以定义同步器中使用的寄存器级数。可选的输入寄存器可以在输入在源时钟域中同步之前对其进行注册。您还可以启用仿真功能以生成消息报告宏的任何潜在误用。注意:此宏假定源数组的每一位都是独立的,没有需要保留的关系。

- 自己尝试过不相关数据合并,其中一个数据只保持一个原时钟域的脉冲,这样可能会同步不到目标时钟域

- 需要保证被目标时钟域采样两次或者更多

使用场景:跨时钟域之后,每一个单bit不再变化,类似于对于跨时钟域的配置数据。

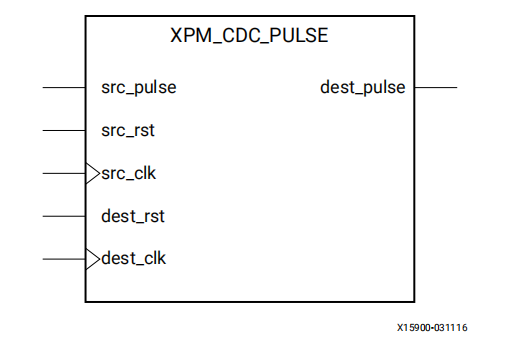

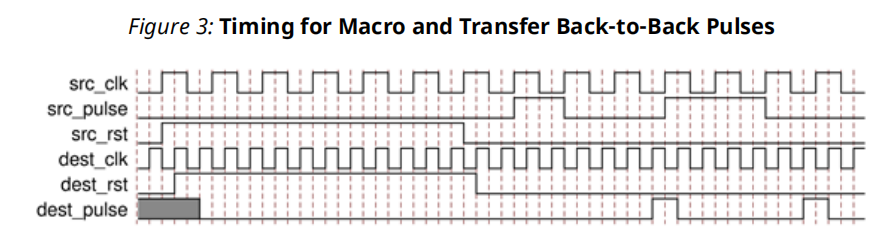

三、XPM_CDC_PULSE

xpm_cdc_pulse #(.DEST_SYNC_FF(4), // DECIMAL; range: 2-10.INIT_SYNC_FF(0), // DECIMAL; 0=disable simulation init values, 1=enable simulation init values.REG_OUTPUT(0), // DECIMAL; 0=disable registered output, 1=enable registered output.RST_USED(1), // DECIMAL; 0=no reset, 1=implement reset.SIM_ASSERT_CHK(0) // DECIMAL; 0=disable simulation messages, 1=enable simulation messages)xpm_cdc_pulse_inst (.dest_pulse(dest_pulse), // 1-bit output: Outputs a pulse the size of one dest_clk period when a pulse// transfer is correctly initiated on src_pulse input. This output is// combinatorial unless REG_OUTPUT is set to 1..dest_clk(dest_clk), // 1-bit input: Destination clock..dest_rst(dest_rst), // 1-bit input: optional; required when RST_USED = 1.src_clk(src_clk), // 1-bit input: Source clock..src_pulse(src_pulse), // 1-bit input: Rising edge of this signal initiates a pulse transfer to the// destination clock domain. The minimum gap between each pulse transfer must be// at the minimum 2*(larger(src_clk period, dest_clk period)). This is measured// between the falling edge of a src_pulse to the rising edge of the next// src_pulse. This minimum gap will guarantee that each rising edge of src_pulse// will generate a pulse the size of one dest_clk period in the destination// clock domain. When RST_USED = 1, pulse transfers will not be guaranteed while// src_rst and/or dest_rst are asserted..src_rst(src_rst) // 1-bit input: optional; required when RST_USED = 1);

此宏将源时钟域中的脉冲同步到目标时钟域。源时钟域中任意大小的脉冲,如果正确启动,将生成一个与单个目标时钟周期相同大小的脉冲。为了正常工作,输入数据必须被目标时钟采样两次或更多次。您可以定义同步器中使用的寄存器级数。可选的源和目标复位可用于重置脉冲传输逻辑。您还可以启用仿真功能,生成报告宏可能被滥用的消息。此宏的实现需要一些反馈逻辑。在没有可选复位信号的情况下模拟宏时,输入脉冲信号(src_pulse)必须始终定义,因为没有复位逻辑可以从宏中传播的未定义或‘x’恢复。

最小间隔是测量src_pulse的下降沿到下一个src_pulse的上升沿之间的距离。这个最小间隔将保证每个src_pulse的上升沿将在目标时钟域生成一个dest_clk周期大小的脉冲。

- 脉冲之间是有一定间隔才能正常工作

- 保证被目标时钟域采样两次(猜测里面是使用脉冲展宽,因为我没有小于两次也生成了目标时钟域的脉冲,还是听官方的吧,这样才能靠谱的正常工作)

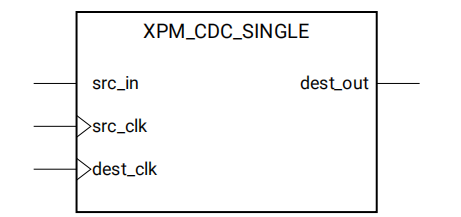

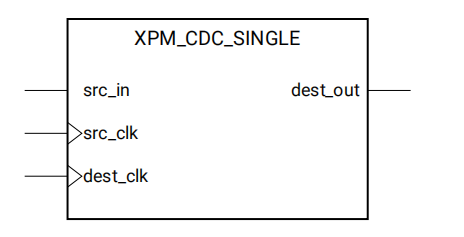

四、 XPM_CDC_SINGLE

xpm_cdc_single #(.DEST_SYNC_FF(4), // DECIMAL; range: 2-10.INIT_SYNC_FF(0), // DECIMAL; 0=disable simulation init values, 1=enable simulation init values.SIM_ASSERT_CHK(0), // DECIMAL; 0=disable simulation messages, 1=enable simulation messages.SRC_INPUT_REG(1) // DECIMAL; 0=do not register input, 1=register input)xpm_cdc_single_inst (.dest_out(dest_out), // 1-bit output: src_in synchronized to the destination clock domain. This output is// registered..dest_clk(dest_clk), // 1-bit input: Clock signal for the destination clock domain..src_clk(src_clk), // 1-bit input: optional; required when SRC_INPUT_REG = 1.src_in(src_in) // 1-bit input: Input signal to be synchronized to dest_clk domain.);

此宏将一个比特信号从源时钟域同步到目标时钟域。为了正常工作,输入数据必须被目标时钟采样两次或更多次。您可以定义同步器中使用的寄存器级数。可选的输入寄存器可用于在同步之前对源时钟域中的输入进行寄存。

- 电平信号一般也能被采样两次,只要满足都可以使用这个来做跨时钟

五、 xpm_cdc_sync_rst

xpm_cdc_sync_rst #(.DEST_SYNC_FF(4), // DECIMAL; range: 2-10.INIT(1), // DECIMAL; 0=initialize synchronization registers to 0, 1=initialize synchronization// registers to 1.INIT_SYNC_FF(0), // DECIMAL; 0=disable simulation init values, 1=enable simulation init values.SIM_ASSERT_CHK(0) // DECIMAL; 0=disable simulation messages, 1=enable simulation messages)xpm_cdc_sync_rst_inst (.dest_rst(dest_rst), // 1-bit output: src_rst synchronized to the destination clock domain. This output// is registered..dest_clk(dest_clk), // 1-bit input: Destination clock..src_rst(src_rst) // 1-bit input: Source reset signal.);

此宏将复位信号同步到目标时钟域。与XPM_CDC_ASYNC_RST宏不同,生成的输出将在目标时钟域中同步断言和解除断言。为了正常工作,输入数据必须被目标时钟采样两次或更多次。您可以定义同步器中使用的寄存器级数以及配置后的初始寄存器值。您还可以启用仿真功能,以生成报告宏可能被误用的消息。

总结

对于上面所有的xpm,都是输入数据必须被目标时钟采样两次或更多次,也就是快到慢的跨时钟,最好就要时钟单独的脉冲展宽或者握手信号,或者是做fifo或者ram缓冲等手段来做跨时钟。