牛客 verilog入门 VIP

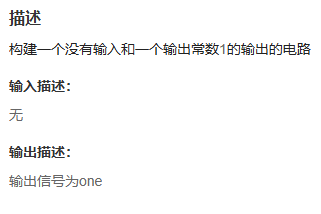

1、输出1

答案:

`timescale 1ns/1nsmodule top_module(output wire one

);assign one = 1'b1;

endmodule2、wire连线

答案:

`timescale 1ns/1nsmodule wire0(input wire in0,output wire out1

);assign out1 = in0;

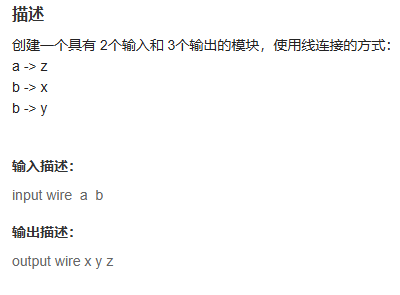

endmodule3、多wire连线

`timescale 1ns/1nsmodule top_module(input wire a,input wire b,output wire x,output wire y,output wire z

);assign z = a;

assign x = b;

assign y = b;endmodule4、反相器

答案:

`timescale 1ns/1nsmodule top_module(input in,output out

);assign out = ~in;

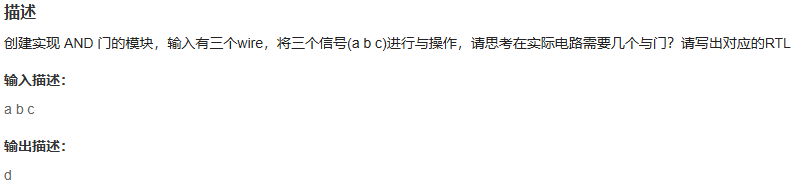

endmodule5、与门

答案:

`timescale 1ns/1ns

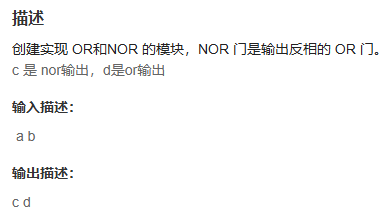

module top_module( input a, input b, input c,output d );wire temp;and gate(temp, a, b);and gate(d, temp, c);endmodule6、NOR门

答案:

`timescale 1ns/1nsmodule top_module( input a, input b, output c,output d);or gate(d, a, b);not gate(c, d);

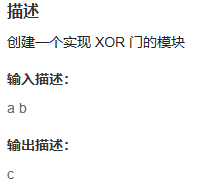

endmodule7、XOR门

答案:

`timescale 1ns/1nsmodule top_module( input a, input b, output c );assign c = a^b;

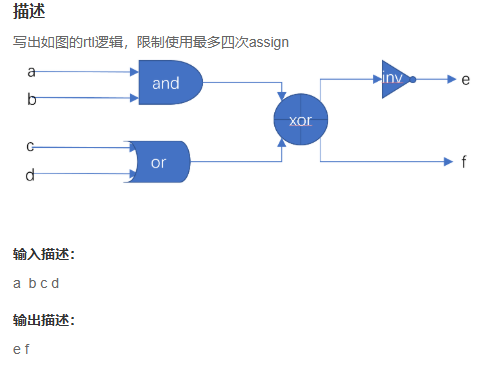

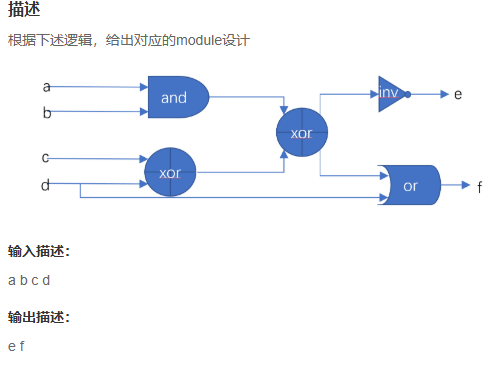

endmodule8、逻辑运算

答案:

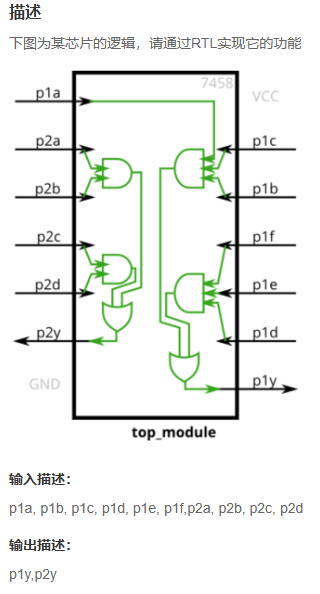

`timescale 1ns/1nsmodule top_module (input a,input b,input c,input d,output e,output f );wire out1, out2;assign out1 = a & b;assign out2 = c | d;assign f = out1 ^ out2;assign e = ~f;endmodule9、模拟逻辑芯片

答案:

`timescale 1ns/1nsmodule top_module ( input p1a, p1b, p1c, p1d, p1e, p1f,output p1y,input p2a, p2b, p2c, p2d,output p2y );wire out1, out2, out3, out4;assign out1 = p2a & p2b;assign out2 = p1a & p1c & p1b;assign out3 = p2c & p2d;assign out4 = p1f & p1e & p1d;assign p1y = out2 | out4;assign p2y = out1 | out3;endmodule10、逻辑运算2

答案:

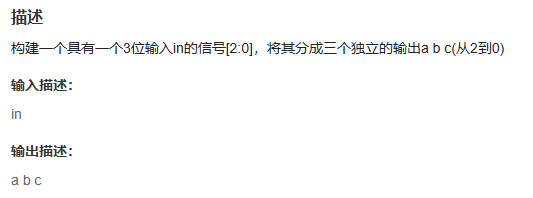

`timescale 1ns/1nsmodule top_module (input a,input b,input c,input d,output e,output f );wire out1, out2, out3;assign out1 = a & b;assign out2 = c ^ d;assign out3 = out1 ^ out2;assign f = out3 | d;assign e = ~out3;endmodule11、多位信号

答案:

`timescale 1ns/1nsmodule top_module(input wire [2:0] in,output a,b,c

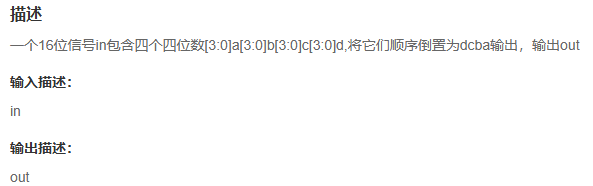

);assign a = in[2];assign b = in[1];assign c = in[0];endmodule12、信号顺序调整

答案:

`timescale 1ns/1nsmodule top_module(input [15:0] in,output out

);assign out = {in[3:0], in[7:4], in[11:8], in[15:11]};endmodule13、位运算与逻辑运算

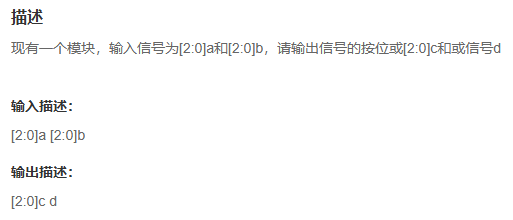

答案:

`timescale 1ns/1nsmodule top_module(input [2:0] a, input [2:0] b, output [2:0] c,output d

);assign c = a | b;assign d = a || b;endmodule14、对信号按位操作

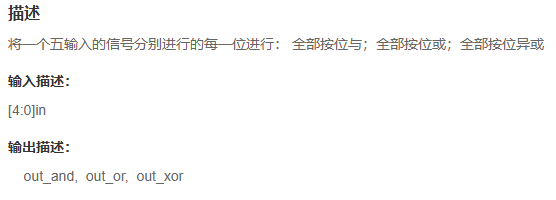

答案:

`timescale 1ns/1nsmodule top_module( input [4:0] in,output out_and,output out_or,output out_xor

);assign out_and = &in[4:0];assign out_or = |in[4:0];assign out_xor = ^in[4:0];endmodule15、信号级联合并

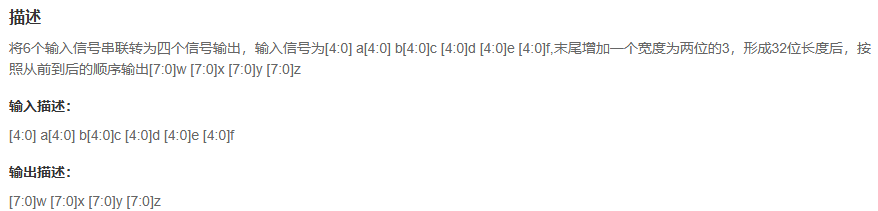

答案:

`timescale 1ns/1nsmodule top_module(input [4:0] a, b, c, d, e, f,output [7:0] w, x, y, z );wire [31:0] out;assign out = {a, b, c, d, e, f, {2'b11}};assign w = out[31:24];assign x = out[23:16];assign y = out[15:8];assign z = out[7:0];endmodule16、信号反转输出

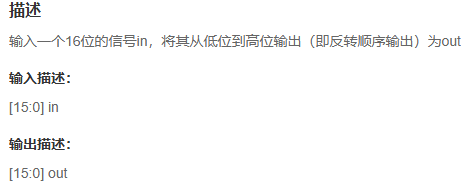

答案:

`timescale 1ns/1nsmodule top_module(input [15:0] in,output [15:0] out

);genvar i;

generatefor(i = 0; i < 16; i = i + 1) beginassign out[i] = in[15-i];end

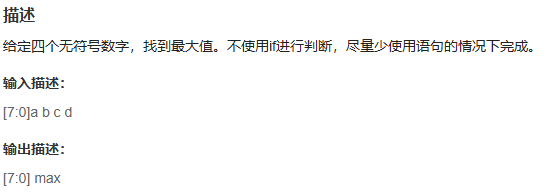

endgenerateendmodule17、三元操作符

答案:

`timescale 1ns/1nsmodule top_module(input [7:0] a, b, c, d,output [7:0] max);//wire [7:0] temp1, temp2;assign temp1 = (a > b)? a : b;assign temp2 = (temp1 > c)? temp1 : c;assign max = (temp2 > d)? temp2 : d;endmodule18、 多位信号xnor

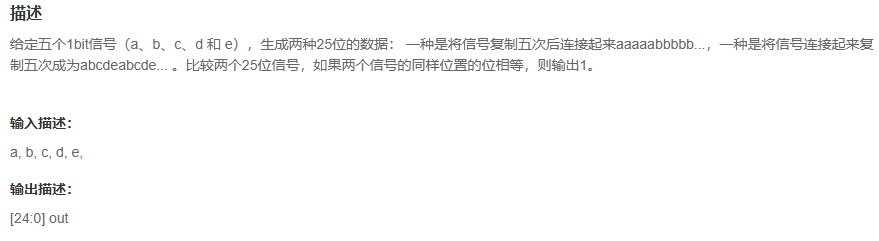

答案:

`timescale 1ns/1nsmodule top_module(input a, b, c, d, e,output [24:0] out

);wire [24:0] temp1, temp2;assign temp1 = {{5{a}}, {5{b}}, {5{c}}, {5{d}}, {5{e}}};

assign temp2 ={5{a,b,c,d,e}};assign out = ~(temp1 ^ temp2);endmodule

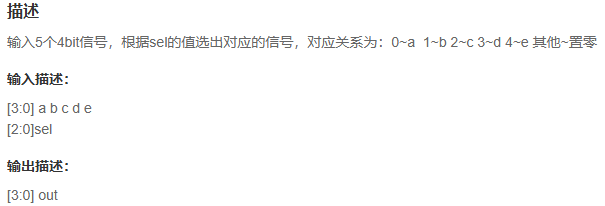

19、五到一选择器

答案:

`timescale 1ns/1nsmodule top_module( input [3:0] a, b, c, d, e, input [2:0] sel,output reg [3:0] out );always @(*)beginout = (sel == 0)? a : (sel == 1)? b : (sel == 2)? c : (sel == 3)? d : (sel == 4)? e : 4'b0;endendmodule20、 256选1选择器

答案:

`timescale 1ns/1nsmodule top_module (input [255:0] in,input [7:0] sel,output out

);assign out = in[sel];endmodule