LVDS系列9:Xilinx 7系可编程输入延迟(二)

使用IDELAYE2的同时,还必须要例化IDELAYCTRL原语,IDELAYCTRL原语为IDELAYE2原语提供时钟参考,同时持续校准各个延迟抽头,减少外部环境和器件对于延迟精度的影响;

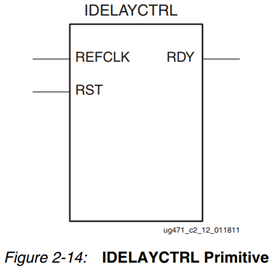

IDELAYCTRL框图

IDELAYCTRL例化模板:

(* IODELAY_GROUP = <iodelay_group_name> *) // Specifies group name for associated IDELAYs/ODELAYs and IDELAYCTRL

IDELAYCTRL IDELAYCTRL_inst (

.RDY(RDY), // 1-bit output: Ready output

.REFCLK(REFCLK), // 1-bit input: Reference clock input

.RST(RST) // 1-bit input: Active high reset input

);

IDELAYCTRL使用:

RST:高电平异步复位,在上电配置后需复位,复位需要在参考时钟REFCLK稳定情况下至少52ns复位;

REFCLK:参考时钟,范围按上一节IDELAYE2的参考时钟范围190.0-210.0, 290.0-310.0选取即可,支持200MHz和300MHz,其中范围有加减10M的范围是原语允许的波动,且该时钟必须由全局BUFG或水平BUFH时钟缓冲器进行驱动;

RDY:准备就绪信号,高有效,指示IDELAY和ODELAY校准完毕。REFCLK如果出现异常如保持一个周期的1或0,RDY就会拉低,此时就需要重新复位该原语;

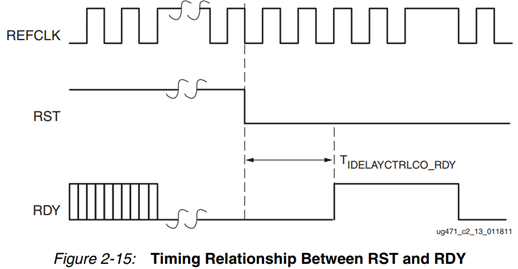

时序如下图所示:

RST复位后,等待一段时间,RDY拉高,表示校准完毕,当REFCLK出现持续的异常高时,RDY拉低。

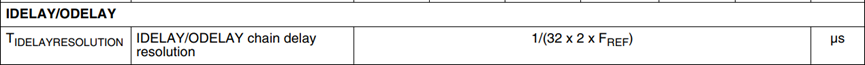

IDELAYE2延时精度:

延时精度指延时抽头值每个tap表示的延迟时间,可以按下列式子计算:

T_tap = 1s/(322REFCLK)

当提供200MHz的参考时钟:

T_tap= 1000000000000ps/(322200000000) = 78.125ps ≈ 78ps

当提供300MHz的参考时钟:

T_tap= 1000000000000ps/(322300000000) = 52.083ps ≈ 52ps

这表示每递增(不环绕的情况下)一个抽头值,数据线的延迟比上一个抽头值的延迟时间增加78ps或52ps;

IDELAY延时值:

IDELAY延时 = 延时基准T_base + 抽头值tap_num*T_tap

其中延时基准T_base一般为600ps,表示数据线只要通过IDELAY原语,即使抽头值为0,也会被延时600ps;

IDELAYE2和IDELAYCTRL仿真测试:

Testbench代码:

Testbench简单生成测试的输入数据和参考时钟,后续在测试模块中修改参数和逻辑去查看原语的各种使用细节;

tb代码:

`timescale 1ns / 1ps

module tb;

reg clk_200m;

reg clk_300m;

reg clk;

reg rst;

reg load_trg;

reg data1;

reg data2;

wire dout;

initial begin

clk_200m = 0;

clk_300m = 0;

clk = 0;

rst = 1;

#200

rst = 0;

end

always #5 clk = ~clk;

always #(2.5) clk_200m = ~clk_200m;

always #(1.667) clk_300m = ~clk_300m;

initial begin

data1 = 0;

data2 = 0;

while(1)begin

#10

data1 = $random();

data2 = $random();

end

end

initial begin

load_trg = 0;

while(1)begin

#100

@(posedge clk)

load_trg = 1;

@(posedge clk)

load_trg = 0;

end

end

top_7series_idelay inst_top_7series_idelay (

.clk_ref_200m (clk_200m),

.clk_ref_300m (clk_300m),

.clk (clk),

.rst (rst),

.load_trg (load_trg),

.idatain (data1),

.datain (data2),

.dout (dout)

);

endmodule

FIXED模式使用:

Fixed模式下的测试模块代码:

module top_7series_idelay(

input wire clk_ref_200m,

input wire clk_ref_300m,

input wire clk,

input wire rst,

input wire load_trg,

input wire idatain,

input wire datain,

output wire dout

);

wire idelayctrl_rdy;

wire [4:0] cntvalueout;

// idelayctrl -------------------------------------------------

IDELAYCTRL IDELAYCTRL_inst (

.RDY(idelayctrl_rdy), // 1-bit output: Ready output

.REFCLK(clk_ref_200m), // 1-bit input: Reference clock input

.RST(rst) // 1-bit input: Active high reset input

);

// idelaye2 -------------------------------------------------

IDELAYE2 #(

.CINVCTRL_SEL(“FALSE”), // Enable dynamic clock inversion (FALSE, TRUE)

.DELAY_SRC(“IDATAIN”), // Delay input (IDATAIN, DATAIN)

.HIGH_PERFORMANCE_MODE(“FALSE”), // Reduced jitter (“TRUE”), Reduced power (“FALSE”)

.IDELAY_TYPE(“FIXED”), // FIXED, VARIABLE, VAR_LOAD, VAR_LOAD_PIPE

.IDELAY_VALUE(0), // Input delay tap setting (0-31)

.PIPE_SEL(“FALSE”), // Select pipelined mode, FALSE, TRUE

.REFCLK_FREQUENCY(200.0), // IDELAYCTRL clock input frequency in MHz (190.0-210.0, 290.0-310.0).

.SIGNAL_PATTERN(“DATA”) // DATA, CLOCK input signal

)

IDELAYE2_inst (

.CNTVALUEOUT(cntvalueout), // 5-bit output: Counter value output

.DATAOUT(dout), // 1-bit output: Delayed data output

.C(0), // 1-bit input: Clock input

.CE(0), // 1-bit input: Active high enable increment/decrement input

.CINVCTRL(0), // 1-bit input: Dynamic clock inversion input

.CNTVALUEIN(0), // 5-bit input: Counter value input

.DATAIN(datain), // 1-bit input: Internal delay data input

.IDATAIN(idatain), // 1-bit input: Data input from the I/O

.INC(0), // 1-bit input: Increment / Decrement tap delay input

.LD(0), // 1-bit input: Load IDELAY_VALUE input

.LDPIPEEN(0), // 1-bit input: Enable PIPELINE register to load data input

.REGRST(0) // 1-bit input: Active-high reset tap-delay input

);

Endmodule

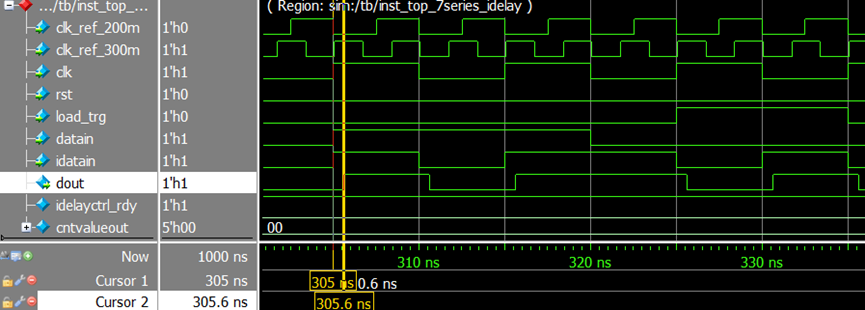

此时idelayctrl使用外部的rst复位,当rdy拉高后我们查看延时情况;

此时使用IDATAIN端口的数据进行延时,选择200M参考时钟,其他模式的控制此时端口不用关注,因为fixed模式不使用动态控制;

可以看到上图中,此时IDELAY_VALUE设置为0,此时cntvalueout为0,表示此时原语正在工作的抽头值为0,idatain和dout的两个上升沿间隔了0.6ns,也就是之前所讲的200M的延时基准;

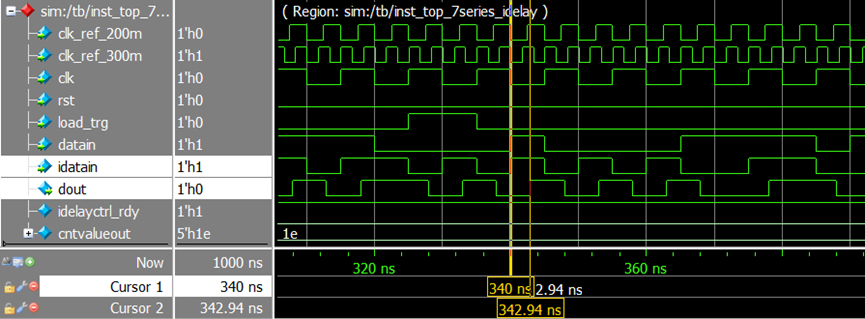

上图为将IDELAY_VALUE参数设置为30(0x1e),此时cntvalueout为0x1e,可以看到此时的idatain和dout的延时为2.94ns=0.6ns+30*78ps,与理论的延时时间相符;

如果将IDELAYCTRL模块的参考时钟改为300M的clk_ref_300m,将IDELAYE2的REFCLK_FREQUENCY参数改为300.0;

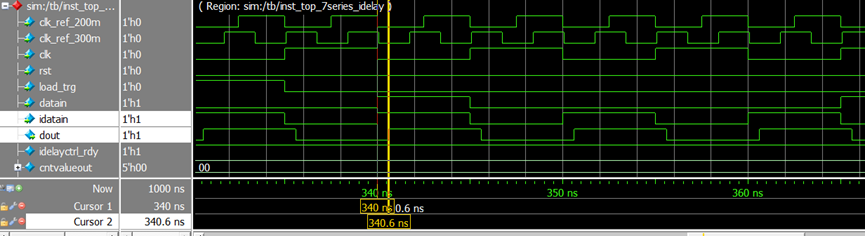

上图为IDELAY_VALUE参数设置为0的情况,可以看到300M参考时钟的情况下,延时基准还是保持为0.6ns;

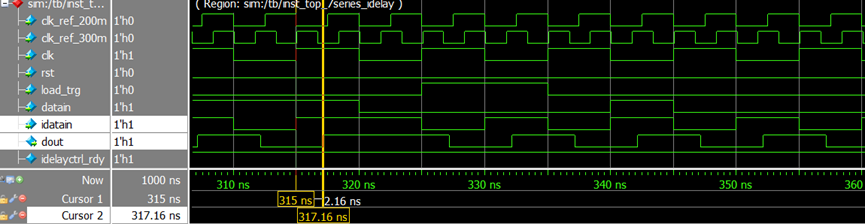

上图为300M参考下,将IDELAY_VALUE参数设置为30(0x1e),可以看到此时的idatain和dout的延时为2.16ns=0.6ns+30*52ps,与理论的延时时间相符;

其他的VARIABLE模式、VAR_LOAD模式和VAR_LOAD_PIPE模式在下一节继续进行讲解;

本文章由威三学社出品

对课程感兴趣可以私信联系