数字IC后端项目典型问题之后端实战项目问题记录(2025.04.24)

今天给大家分享下近两天小编帮助学员解决的几个经典后端项目问题。希望能够对大家的学习和工作有所帮助。

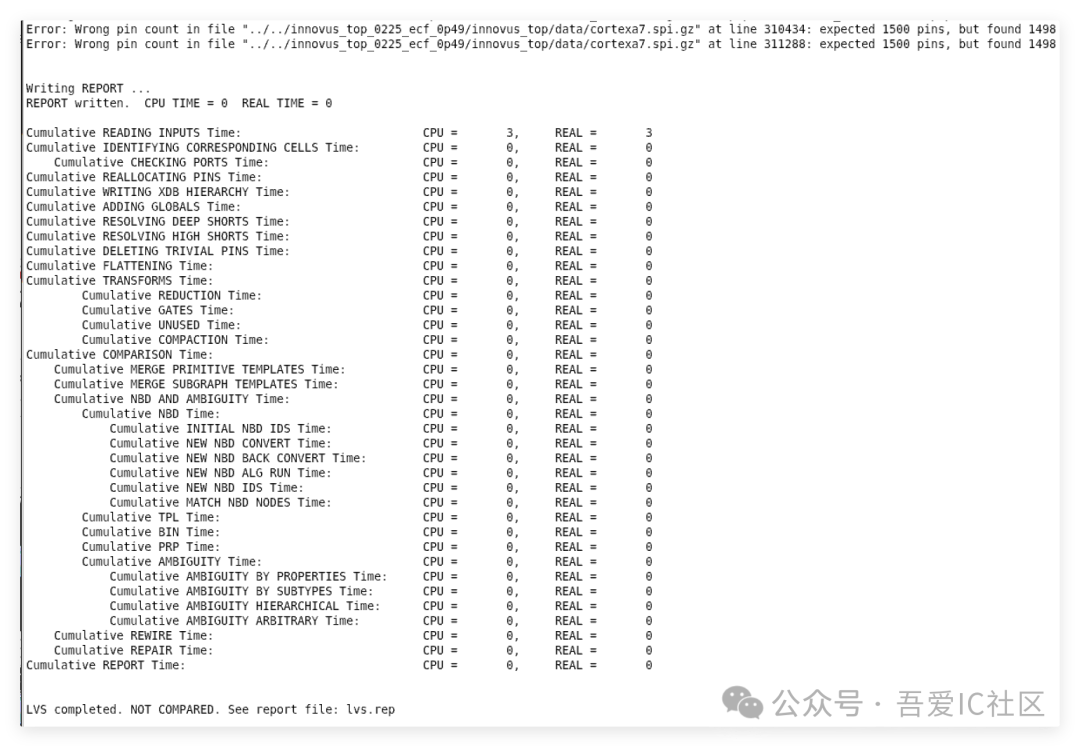

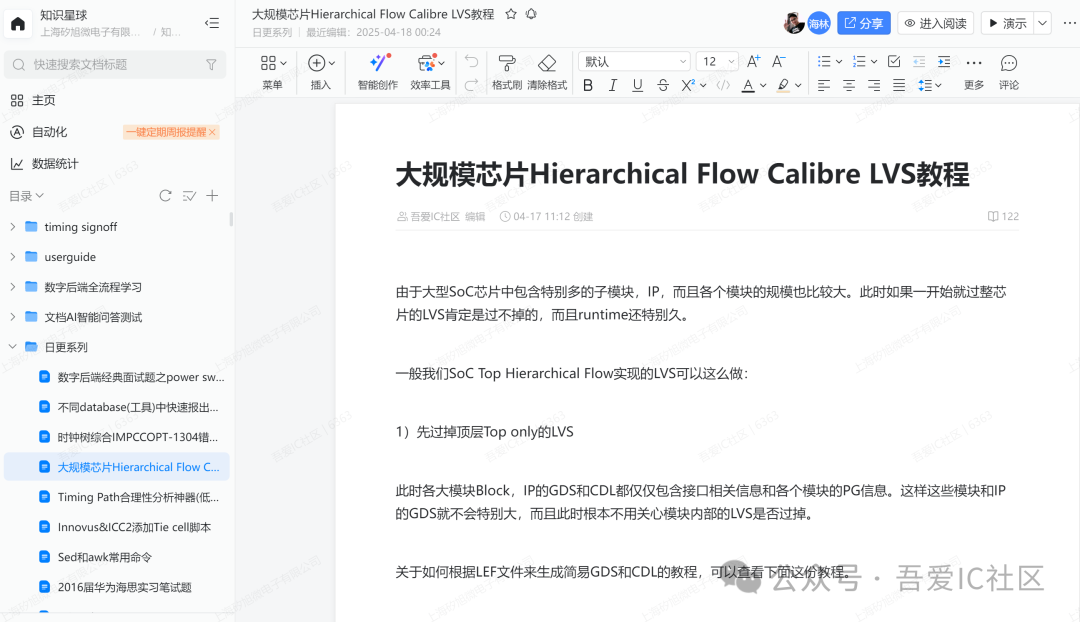

Q1:在做a7top顶层物理验证Calibre LVS检查时提示NOT COMPARED,请问是什么原因?

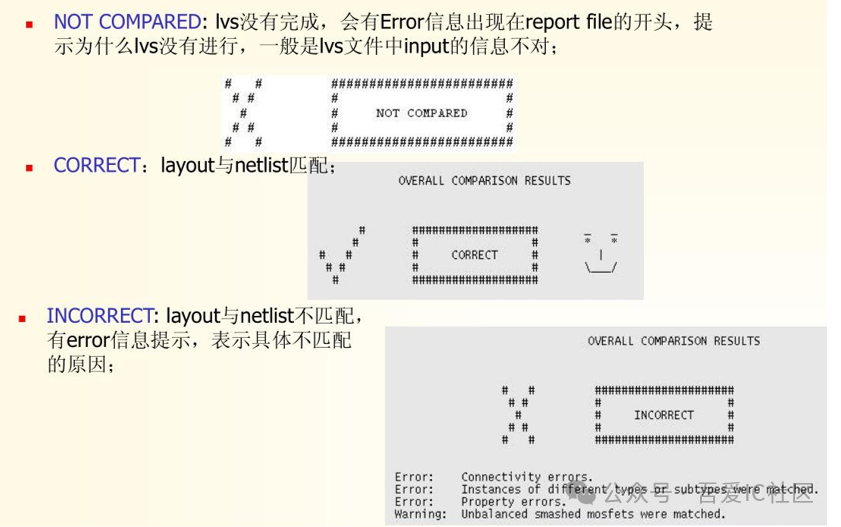

我们在用calibre检查LVS后,其结果基本上就是以下三种情况。

1)NOT COMPARED

这种提示是LVS没有跑成功。建议检查LVS log中的ERROR,一般都是缺东西,比如缺标准单元的spice等。一旦出现这种情况,不要去分析什么LVS了,设计都缺东西,先把缺的文件都补齐了,然后再跑LVS。

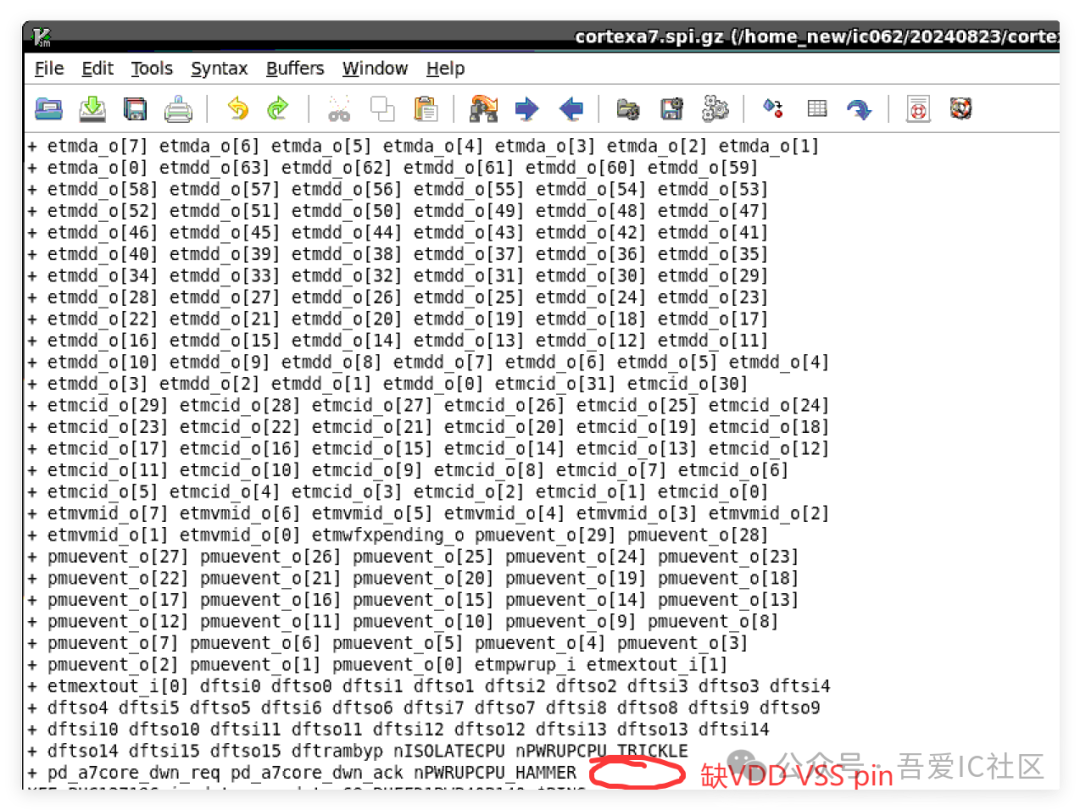

本案例是子模块cortexa7core的SUBCKT缺VDD和VSS port。

2)CORRECT

这种情况就是layout与netlist是匹配的。除了看这个笑脸外,我们还需要仔细查看layout抽取的report。

3)INCORRECT

解决source netlist问题后,我们重新跑LVS后的结果出现INCORRECT。

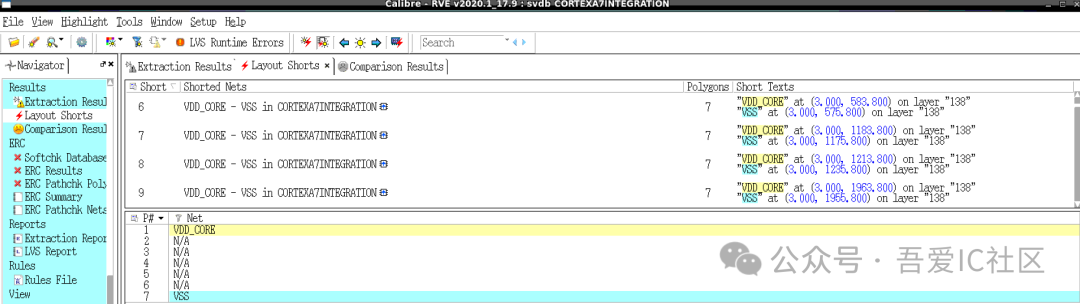

首先,我们在innovus中加载Calibre LVS的short报告,这里提示存在VDD_CORE和VSS的PG Short。

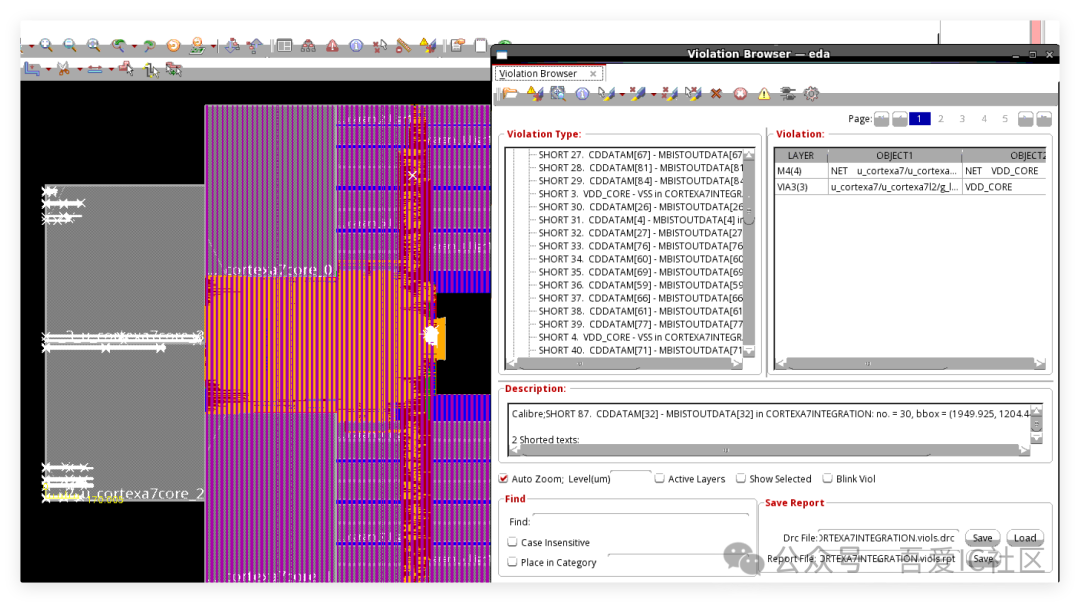

在Innovus中放大short高亮位置,我们发现并没有顶层的PG Short。

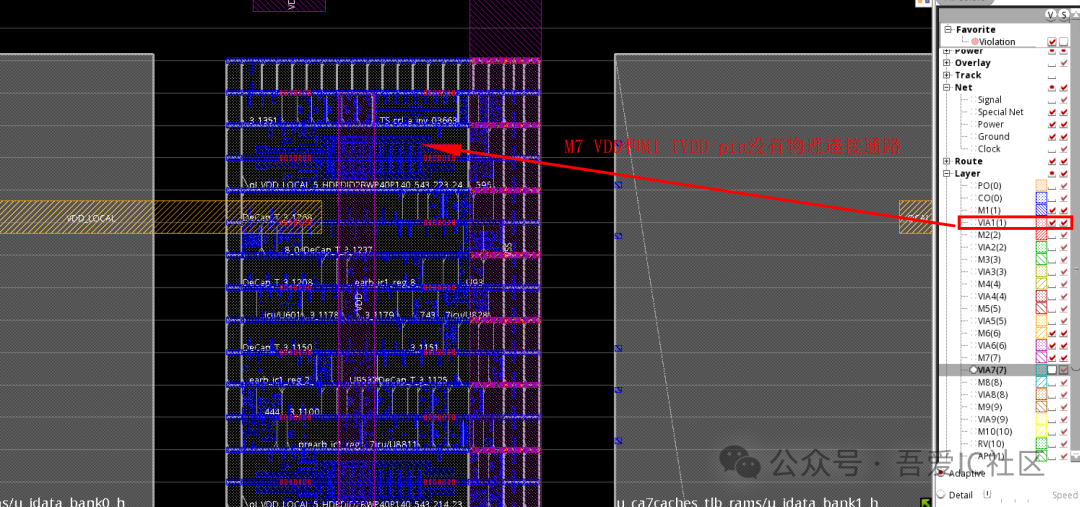

这时候我们有理由怀疑子模块内部可能使用了高层的metal。

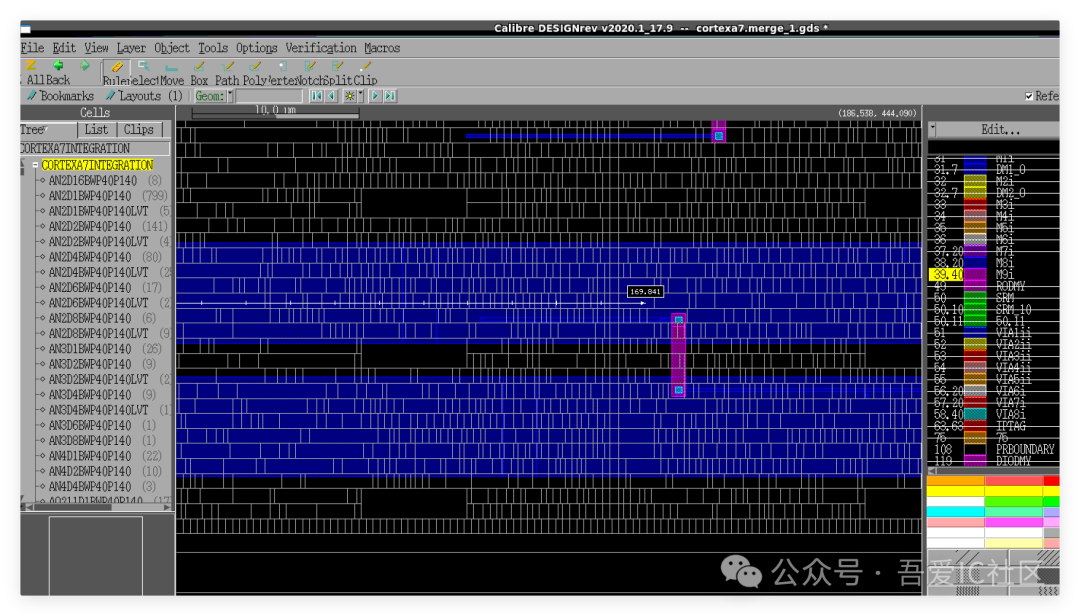

所以,我们打开a7top merge好子模块的GDS查看,经过定位发现这个位置的确有一根M9的VSS横跨在两根M8的VDD_CORE和VSS。

数字IC后端设计实现之Innovus自动修复Min Step DRC Violation方案

这也是为什么我们训练营项目在做子模块a7core时只能使用M2-M6进行signal routing,PG最高层只能用到M7。

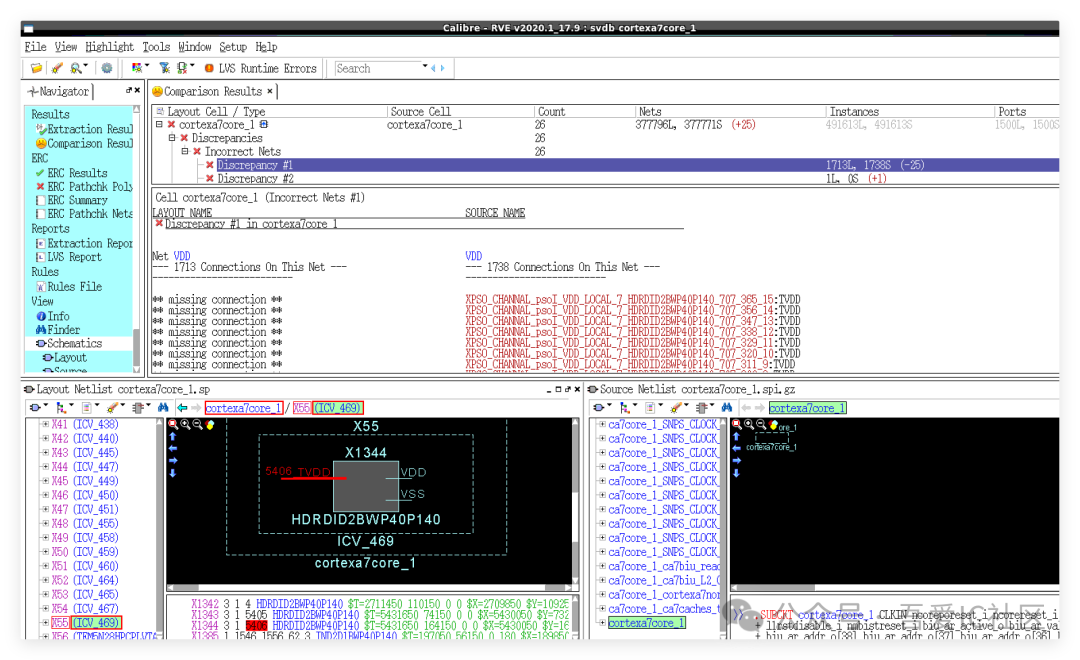

解决掉这个PG Short后,继续跑Calibre LVS,发现存在如下所示的Incorrect Net问题。

看到这里基本上可以判断出power switch cell的global pg pin TVDD存在open的情况。定位到Innovus中可以清晰看到TVDD Pin open的情况。

手把手教你debug解决数字IC后端物理验证Calibre LVS错误

更多关于芯片顶层Calibre LVS方面的教程,可以前往钉钉后端知识库查看。

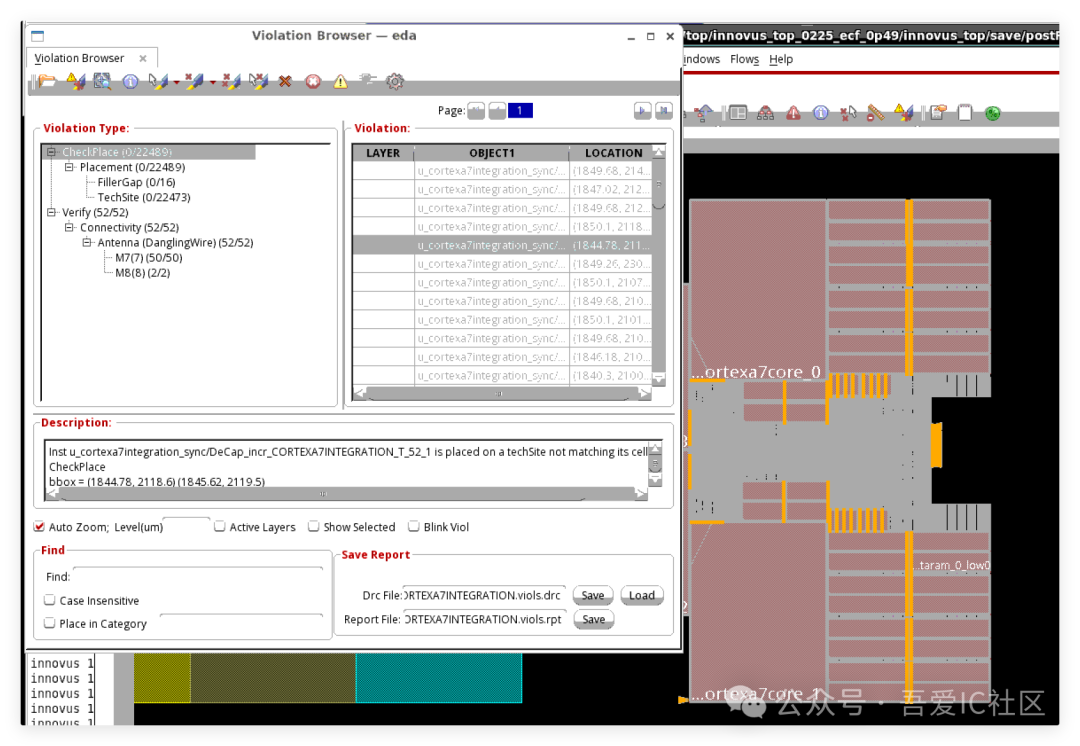

Q2: checkPlace检查报告出来的TechSite Violation是怎么回事?应该如何解决?

这个错误其实是提示当前设计中添加的ECO Filler没有摆放到它自己所属的site row上。本质原因是学员在做floorplan时没有给设计创建GDCAP cell对应的row。

更多关于checkPlace violation的介绍,可以查看如下所示教程。

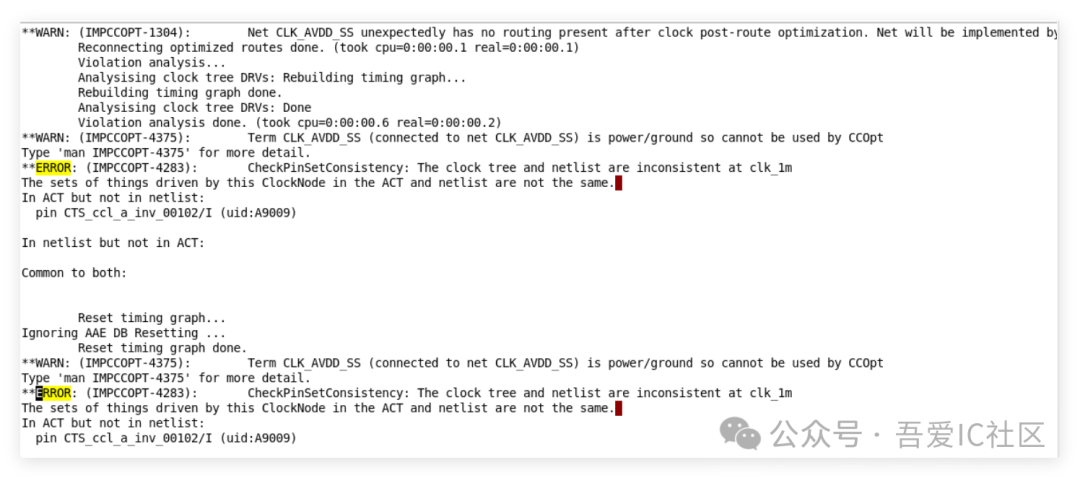

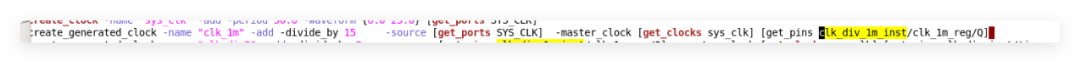

Q3: 有学员在做公司自己项目CTS时发现跑不下去,报了如下所示的错误IMPCCOPT-4375。

第一次遇到这种错误,其实可以从提示信息上入手。

Term CLK_AVDD_SS is power /ground (这个信息非常重要)!也就是说ccopt engine发现这个port是接到电源地的,但是你又要让它做clock tree,这不是明显为难它吗?

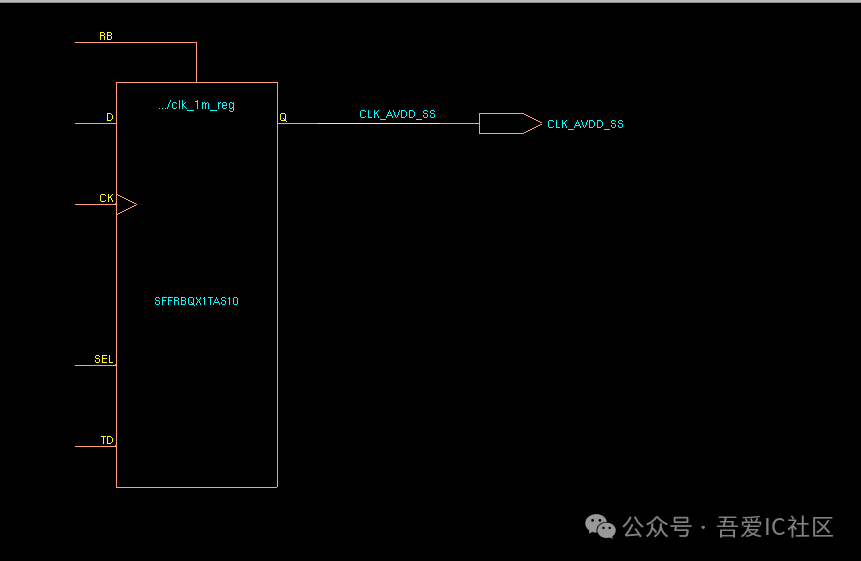

所以我们选中一个io port,看看它的逻辑连接。trace连接关系后如下图所示,clk_1m_reg的输出直接送到这个io clock port。

稍微有经验的后端工程师,应该可以判断出这个寄存器必须定义generated clock,否则这里就一定会漏clock tree。

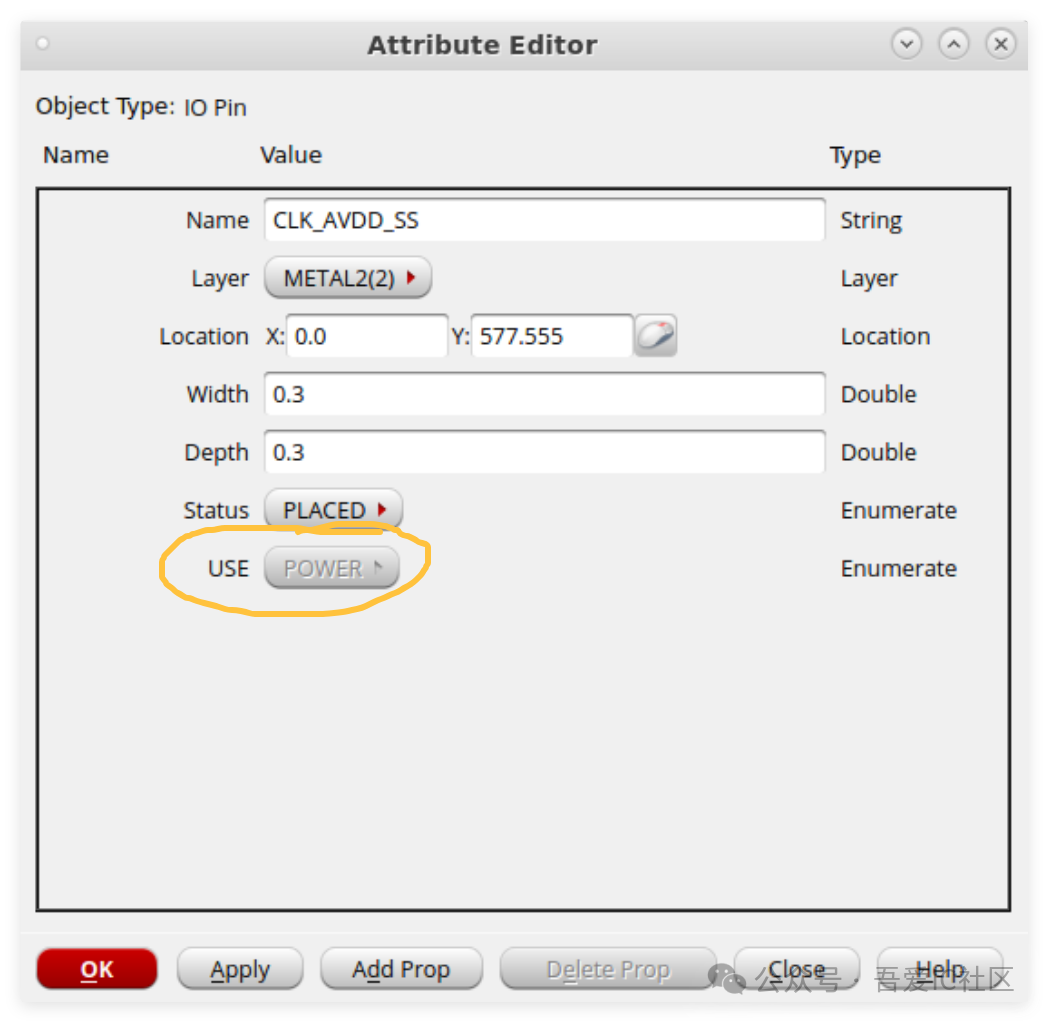

从逻辑关系上看,这里的确没啥毛病。这时候就剩一种可能性了——io port的属性问题了!

选中这个io port,右键查看它的属性,我们马上就可以看到这个port有Power属性!到这里我们就找到问题了。

只需要把模拟版图工程师提供的def文件中的这个io port的USE类型改成普通信号类型即可。更改后重新跑下CTS就可以正常做完时钟树综合。

Q4: Power Switch cell在串链以后,如果出现的max trans的问题,要怎么解决?或者说有没有做过在PD_PSO domain插always-on buf的经历?怎么做的?

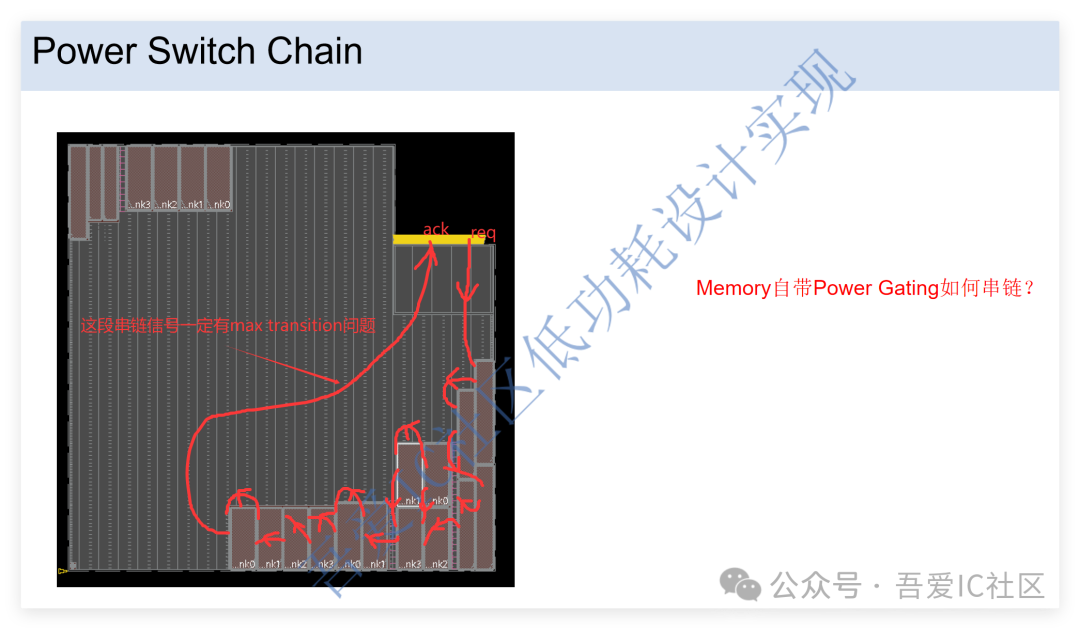

下图所示为咱们社区T28nm a7core power switch cell串链后的示意图,图中白色高亮的为我们floorplan添加的power switch cell。

为了保证电源开关power switch cell chain(NSLEEP)信号的transition满足signoff要求,我们在串链的时候就需要保证相邻两个power switch cell的距离是最近的。

我们知道这类信号是always on 信号,当cpu power off时它还必须是on的。所以串链信号出现max transition问题,中间也不能插普通buffer或inverter,而是应该插always on buffer来解决。

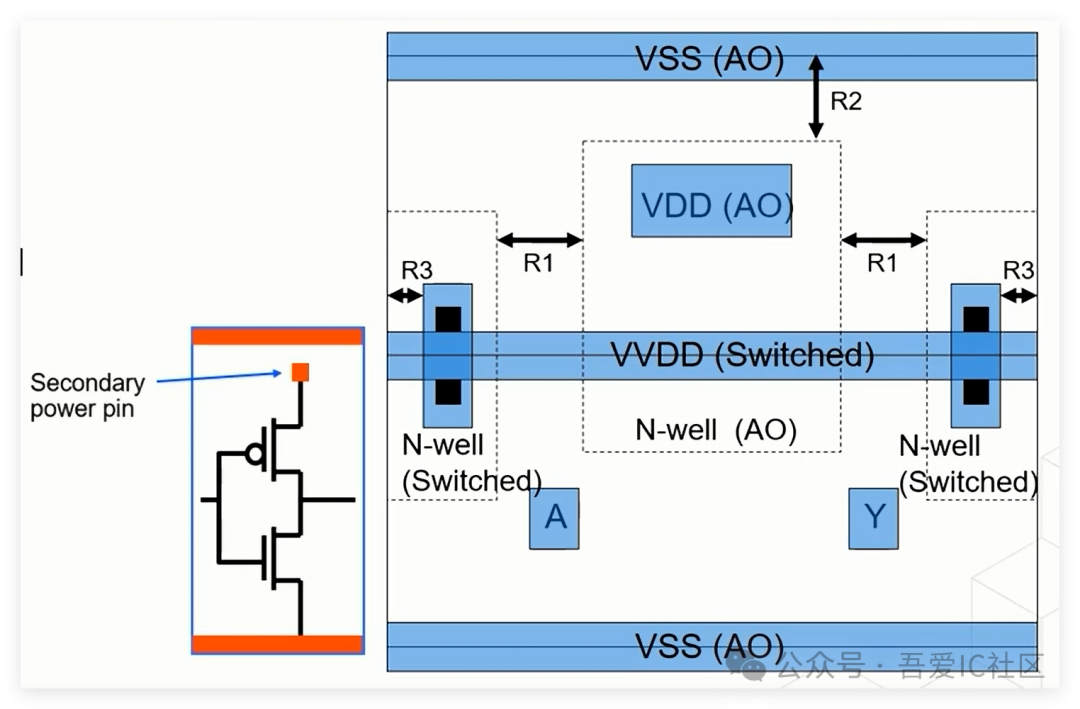

AON Buffer的结构如下图所示,它包含VSS,VVDD和VDD PG Pin。

插always on buffer有两个实现方式:

1)手工针对存在max transition net来插我们PR 默认flow都会把aon buffer设置成dont use属性。

所以,首先我们需要把aon buffer的dont use属性去掉。然后使用传统插buffer的命令ecoAddRepeater,指定插入always on buffer cell即可。

- 通过低功耗upf告诉工具串链信号的power domain属性

由于串链逻辑连接在netlist中是不存在的,所以我们需要先创建所有power switch cell之间的逻辑连接。然后也是需要remove掉aon buffer的dont use属性。

这样工具在优化时序和timing drv阶段就会在有max transition点插AON Buffer。但这种做法非常依赖工具的算法,通常会引入较多always on buffer,所以很少这么做。

大部分场景还是采用第一种方案——Floorplan阶段就规划好每个power switch cell的连接顺序。

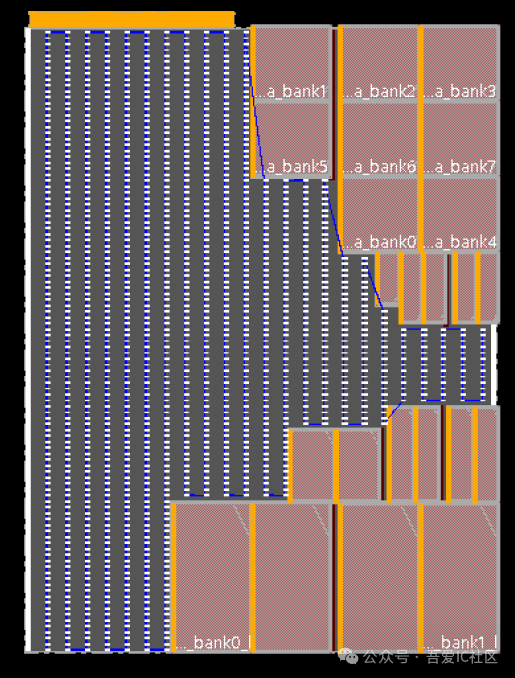

【思考题】对于下图所示的T12nm A55项目,右下角的这些memory做成一个power domain,而且memory本身自带power gating,请问我们应该如何来串memory的chain?