22.晶振的信号与布局布线处理

晶振的信号与布局布线处理

- 1. 晶振电路设计原理图

- 2. 晶振布局布线注意事项

1. 晶振电路设计原理图

(1)无源晶振电路原理图

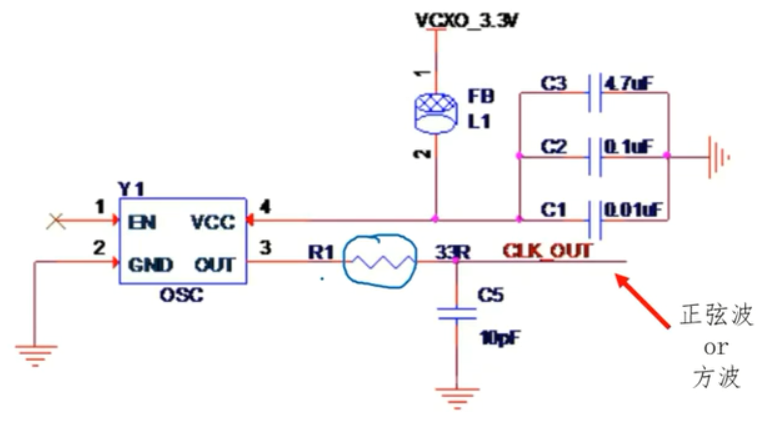

(2)有源晶振电路原理图

(3)晶振电路注意事项总结

- 有源晶振的电源引脚通过一个磁珠后接入电源,可降低电源噪声对时钟输出频率的影响。

- 晶振电源的去耦电容一般选3个,容值依次差一个数量级。去耦电容靠近晶振的电源引脚,按电源流入方向,容值从大到小依次摆放。

- 有源晶振的时钟输出端(方波or正弦波,取决于是否有内部整形电路)串联一个小电阻。如果输出方波,串联电阻可以减少高次谐波,并减少反射和过冲;如果输出正弦波,可以抑制电流,降低辐射能量。

- 晶振外壳接地,抑制晶振向外辐射,也屏蔽外来信号对晶振的干扰。

- 晶振下面不布线,保证完全铺地。晶振300mil内不布线,防止晶振干扰其它布线、器件和层。

- 时钟信号走线尽量短,线宽大一些,并尽量远离发热源。

- 晶振不放置在PCB板边缘,防止边缘辐射。

2. 晶振布局布线注意事项

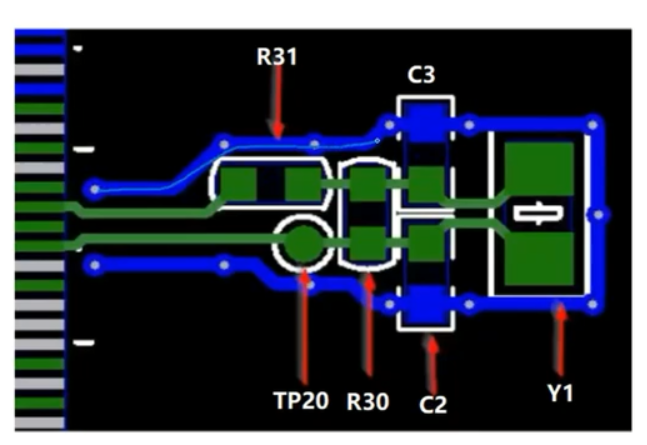

(1)布局注意事项

- 和IC布在同一层面,少打孔;

- 布局紧凑,电容位于晶振和IC之间且靠近晶振,时钟线到IC短;

- 对测试点,避免悬空线或尽量短;避免靠近散热片、导线等。

(2)布线注意事项

- 和IC同层布局同层走线,少打孔,如打孔则在附近加回流地孔;

- 类差分走线;

- 走线要加粗,通常8~12mil;

- 由于晶体始终波形为正弦波,所以此处按模拟设计思路处理;

- 信号线包地处理,且包地线或者铜皮要打屏蔽地孔;

- 晶体电路模块区域相当于模拟区域,不要有其它信号穿过。