Armv9 Cortex-A720的L2 memory system 和 L2 Cache

9 L2 memory system

Cortex-A720核心的L2内存系统通过CPU bridge连接core与DynamIQ Shared Unit-120,其中包括私有的L2缓存。

L2缓存是统一的,每个Cortex-A720核心在一个集群中都有私有的L2缓存。

L2内存系统包括使用虚拟地址(VA)和程序计数器(PC)的数据预取引擎。不同的引擎能够预取L2缓存中的数据。

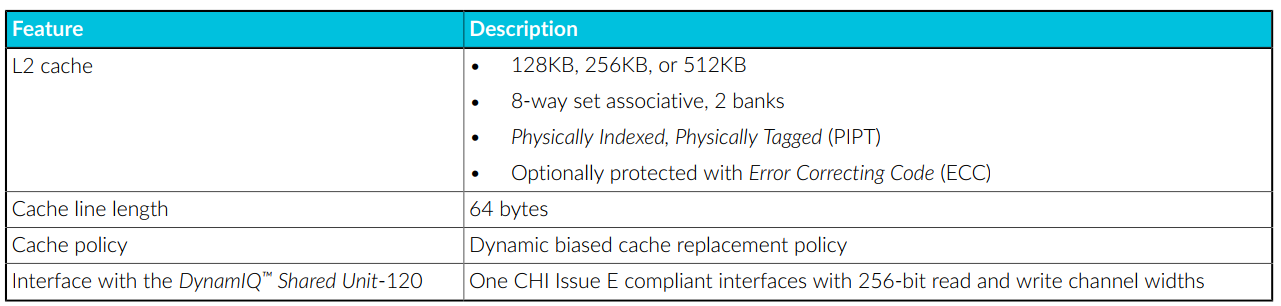

以下表格显示了L2内存系统的特性。

9.1 L2缓存

集成的L2缓存处理来自指令和数据侧的指令和数据请求,以及 translation table walk 请求。

L1指令缓存和L2缓存是weakly inclusive的。在L1指令缓存和L2缓存中未命中的指令获取会分配到两个缓存,但L2缓存的失效不会导致对L1指令缓存的反向失效。

L1数据缓存和L2缓存是strictly exclusive的。在L1数据缓存中包含的任何数据都不会存在于L2缓存中

。

除非将core电源模式初始化为Debug恢复模式,否则L2缓存会在重置时自动失效。

缓存索引的确定方式意味着物理地址(PA)和组编号之间没有直接关系。不能使用假设PA和组编号之间存在关系的有针对性的操作。要刷新整个缓存,必须根据缓存的CCSIDR_EL1描述的组和方式数量执行组和方式维护操作。此操作符合Armv8-A架构。

9.2 内存类型支持

Cortex-A720核心通过将某些内存类型降级来简化一致性逻辑: