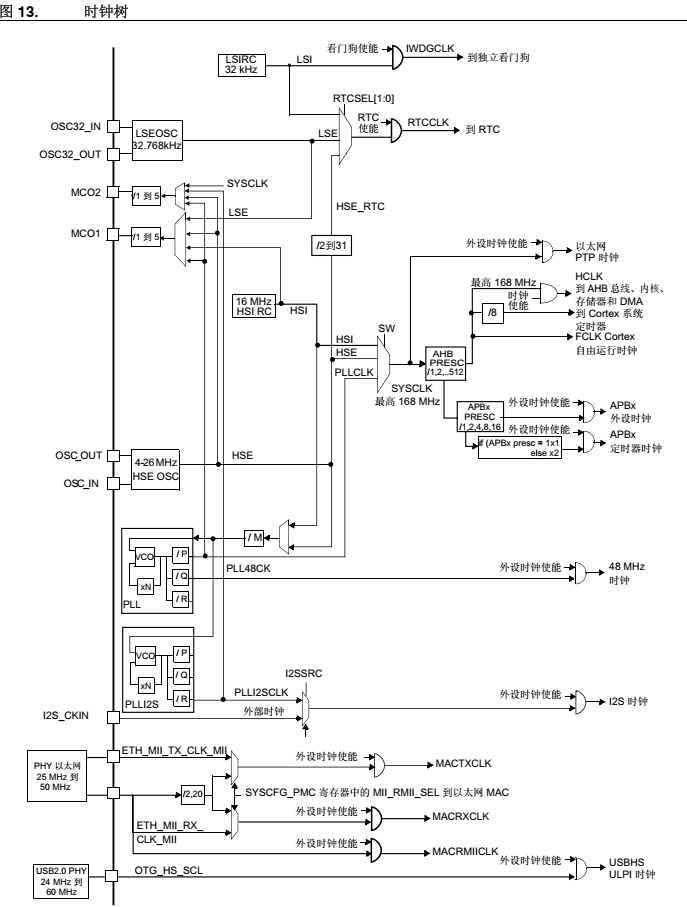

STM32F429 的时钟系统,从AHB到APB1和APB2再到外设

STM32F429 的时钟系统是其核心架构之一,APB1(Advanced Peripheral Bus 1)、APB2(Advanced Peripheral Bus 2) 是连接外设的两条总线,它们与 系统时钟(SYSCLK) 的关系可从时钟来源、分频机制、外设分配三方面深入理解。以下是详细解析:

F429 的标准配置:

• APB1(PCLK1):4 分频(AHB/4=45MHz,满足≤45MHz)

• APB2(PCLK2):2 分频(AHB/2=90MHz,满足≤90MHz)

一、时钟架构总览

1. 核心时钟源

STM32F429 的 系统时钟(SYSCLK) 可来自以下来源(通过 RCC 时钟控制器配置):

- HSI(内部高速时钟):16MHz RC 振荡器,精度较低,用于低速场景。

- HSE(外部高速时钟):外接晶振(如 8MHz),经 PLL 倍频后作为主时钟。

- PLL(锁相环):将 HSE 或 HSI 倍频至最高 180MHz(F429 典型配置),作为系统时钟(SYSCLK)。

2. 总线层次结构

系统时钟(SYSCLK, 180MHz)↓ 分频(AHB 预分频器)

AHB 总线时钟(HCLK, 最大 180MHz)↓ 分频(APB1 预分频器)

APB1 总线时钟(PCLK1, 最大 45MHz)↓ 分频(APB2 预分频器)

APB2 总线时钟(PCLK2, 最大 90MHz)

- AHB(Advanced High-performance Bus):连接高速外设(如 DMA、内存),最高频率等于 SYSCLK(168MHz)。

- APB1(低速总线):连接低速外设(如 UART、I2C1、SPI2),最大频率 45MHz(由芯片规格决定)。

- APB2(高速总线):连接高速外设(如 TIM1、ADC、GPIO 端口),最大频率 90MHz(F429 特性)。

二、APB1 与 APB2 的关键区别

| 特性 | APB1(PCLK1) | APB2(PCLK2) |

|---|---|---|

| 最大频率 | 45MHz(当 SYSCLK=180MHz时,分频系数≥4) | 90MHz(当 SYSCLK=180MHz时,分频系数≥2) |

| 连接外设 | 低速外设(如 TIM2-TIM7、USART2-USART3、I2C1-I2C3) | 高速外设(如 TIM1、TIM8、ADC1-ADC3、GPIOA-GPIOG) |

| 预分频系数 | 可配置为 1、2、4、8、16(通过 RCC_CFGR 的 PPRE1 位) | 可配置为 1、2、4、8、16(通过 RCC_CFGR 的 PPRE2 位) |

| 典型应用 | 低速通信接口、低功耗外设 | 高速定时器、ADC、GPIO 快速翻转 |

三、时钟分频配置(以 SYSCLK=168MHz 为例)

1. AHB 预分频(HCLK = SYSCLK / AHB 分频系数)

- 寄存器:

RCC_CFGR的HPRE位(默认分频系数 1,即 HCLK=180MHz)。 - 配置代码(标准库):

RCC_HCLKConfig(RCC_SYSCLK_Div1); // HCLK = SYSCLK = 180MHz

2. APB1 预分频(PCLK1 = HCLK / APB1 分频系数)

- 分频系数必须≥4 才能保证 PCLK1 ≤42MHz(如

RCC_HCLK_Div4时,PCLK1=180/4=45MHz)。 - 寄存器:

RCC_CFGR的PPRE1位。 - 配置代码:

RCC_PCLK1Config(RCC_HCLK_Div4); // PCLK1 = 180MHz/ 4 = 45MHz

3. APB2 预分频(PCLK2 = HCLK / APB2 分频系数)

- 分频系数必须≥2 才能保证 PCLK2 ≤90MHz(如

RCC_HCLK_Div2时,PCLK2=180/2=90MHz)。 - 寄存器:

RCC_CFGR的PPRE2位。 - 配置代码:

RCC_PCLK2Config(RCC_HCLK_Div2); // PCLK2 = 180MHz/ 2 = 90MHz

四、外设时钟使能与频率获取

1. 使能外设时钟

- APB1 外设(如 TIM2):使用

RCC_APB1PeriphClockCmd。RCC_APB1PeriphClockCmd(RCC_APB1Periph_TIM2, ENABLE); - APB2 外设(如 TIM1):使用

RCC_APB2PeriphClockCmd。RCC_APB2PeriphClockCmd(RCC_APB2Periph_TIM1, ENABLE);

2. 获取当前总线频率(标准库函数)

- 获取 AHB 频率:

SystemCoreClock(定义于system_stm32f4xx.c,默认 180MHz)。 - 获取 APB1 频率:

RCC_GetPCLK1()。 - 获取 APB2 频率:

RCC_GetPCLK2()。

uint32_t pclk1 = RCC_GetPCLK1(); // 返回 APB1 时钟频率(单位:Hz)

uint32_t pclk2 = RCC_GetPCLK2(); // 返回 APB2 时钟频率(单位:Hz)

五、典型外设与总线映射(F429 部分外设)

| 外设类型 | 连接总线 | 示例外设 | 时钟配置注意事项 |

|---|---|---|---|

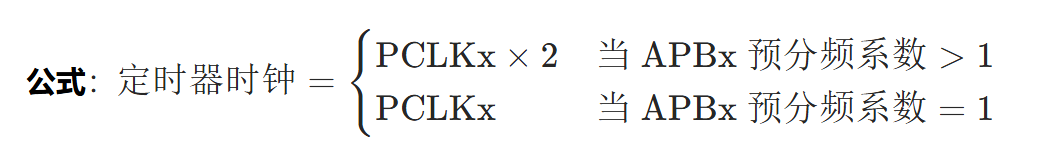

| 高级定时器 | APB2 | TIM1、TIM8(1 80MHz 输入,需分频) | 定时器时钟 = PCLK2 × 2(当 APB 预分频≠1 时) |

| 通用定时器 | APB1 | TIM2-TIM7 | 定时器时钟 = PCLK1 × 2(当 APB 预分频≠1 时) |

| GPIO 端口 | APB2 | GPIOA-GPIOG(除 GPIOH/GPIOI) | 输出速度需匹配 PCLK2 频率 |

| ADC | APB2 | ADC1-ADC3 | 时钟建议 ≤36MHz,需额外分频 |

| UART | APB1/APB2 | USART1(APB2)、USART2(APB1) | 波特率计算基于对应总线频率 |

六、定时器时钟的特殊处理(关键!)

当 APB 总线的预分频系数 ≠1 时,STM32 的 通用定时器(TIMx)和高级定时器(TIM1/TIM8) 的时钟会自动乘以 2,以补偿分频带来的延迟。例如:

- 若 PCLK1=42MHz(APB1 分频系数=4),则 TIM2 定时器时钟=42MHz×2=90MHz。

- 若 PCLK2=84MHz(APB2 分频系数=2),则 TIM1 定时器时钟=84MHz×2=180MHz。

这一特性确保定时器在 APB 分频时仍能保持较高精度,避免因总线分频导致定时误差扩大。

ADCCLK= APB2 总线时钟(PCLK2)/ ADC 分频系数(2、4、6、8)

七、配置最佳实践

-

系统时钟初始化:

上电后优先配置 PLL,将系统时钟设为 180MHz(F429 最高频率),代码参考system_stm32f4xx.c中的SetSysClock()。 -

外设时钟匹配:

- 高速外设(如 TIM1、ADC)连接 APB2,确保 PCLK2=90MHz(分频系数=2)。

- 低速外设(如 UART2)连接 APB1,使用默认分频系数=4(PCLK1=45MHz)。

-

避免频率超限:

- 确保 APB1 频率 ≤45MHz,APB2 频率 ≤90MHz(查看芯片数据手册确认极限参数)。

- ADC 时钟需额外通过

RCC_ADCCLKConfig分频至 ≤36MHz。

-

时钟使能顺序:

先使能总线时钟(如 RCC_AHB1Periph_GPIOE),再初始化外设(如 GPIO_Init),避免寄存器操作时时钟未稳定。

八、总结:

1、时钟关系图

系统时钟(180MHz)

├─ AHB 总线(168MHz,HCLK)

│ ├─ APB2 总线(90MHz,PCLK2)→ 高速外设(TIM1、GPIO、ADC)

│ └─ APB1 总线(45MHz,PCLK1)→ 低速外设(TIM2、UART、I2C)

└─ 其他时钟(如 USB、SDIO 专用时钟)

2、180MHz 系统时钟下的关键配置

外部晶振(HSE,8MHz) → PLL锁相环 → 系统时钟(SYSCLK,最高180MHz)

↓

SYSCLK → AHB总线时钟(HCLK,180MHz)

↓

AHB → APB1总线时钟(PCLK1,最大45MHz)、APB2总线时钟(PCLK2,最大90MHz)

- 系统时钟配置:

◦ 外部晶振 HSE=8MHz,PLL 配置为 M=8, N=360, P=2,得到 SYSCLK=180MHz。

◦ 通过 RCC_PLLCFGR 寄存器设置上述参数,并使能 PLL。 - AHB/APB 总线配置:

◦ AHB=180MHz(不分频)。

◦ APB1=45MHz(4 分频,PPRE1=0b010),APB2=90MHz(2 分频,PPRE2=0b001)。 - 定时器时钟:

◦ TIM1(APB2 外设)时钟 = PCLK2 × 2 = 90MHz × 2 = 180MHz(因 APB2 分频系数 = 2≠1,触发定时器时钟倍频)。

理解 APB1/APB2 与系统时钟的关系是配置外设的基础,尤其是定时器、ADC 等对时钟敏感的模块。通过合理设置预分频系数,可在性能与功耗间取得平衡,确保系统稳定运行。