高效的项目构建:用 Makefile 自动化你的构建过程

前言:📕什么是 Makefile?

Makefile是一种文件格式,用于描述如何通过自动化规则构建、编译和管理项目中的文件。它常配合make工具使用,后者会根据Makefile中定义的规则和依赖关系自动执行相应的构建命令。最初,

Makefile主要用于 C 和 C++ 项目的构建,但它同样适用于其他语言的项目,例如 Java、Python、甚至前端开发中的构建任务。

★ make是一条命令,makefile是一个文件,两个搭配使用,完成项目自动化构建

1. Makefile 的基础:从编写到执行

1.1 创建源代码与 Makefile(需要手动创建一个makefile文件)

我们从创建源代码文件 test.c 和 Makefile 开始:

[jkl@VMCentos7 lesson4]$ touch test.c makefile

[jkl@VMCentos7 lesson4]$ ls

makefile test.c

1.2 编写 Makefile

接着,我们在 Makefile 中编写自动化构建规则:

# Makefile 示例# 定义目标文件和源文件

target = test.exe

source = test.c# 默认目标:编译生成目标文件

$(target): $(source)gcc $(source) -o $(target)# 清理目标:删除编译生成的文件

.PHONY: clean

clean:rm -f $(target)

1.3 编写源代码

然后,我们在 test.c 文件中编写一个简单的 C 语言程序:

#include <stdio.h>int main() {printf("Hello, Linux!\n");return 0;

}

1.4 执行 make 命令

现在,执行 make 命令来自动编译生成目标文件:

[jkl@VMCentos7 lesson4]$ make

gcc test.c -o test.exe

[jkl@VMCentos7 lesson4]$ ls

makefile test.c test.exe

[jkl@VMCentos7 lesson4]$ ./test.exe

Hello, Linux!

通过执行 make 命令,make 工具自动检测到 test.c 文件并进行编译,最终生成了 test.exe 可执行文件。

2. Makefile 的工作原理

当我们执行 make 命令时,make 会遵循以下步骤:

-

make会查找当前目录中的Makefile文件,并读取其中的规则。 -

根据

Makefile中定义的目标文件和依赖关系,make会决定哪些文件需要重新编译,哪些文件已经是最新的。 -

如果目标文件需要重新生成,

make会执行相关的编译命令。

2.1 判断文件是否需要重新编译

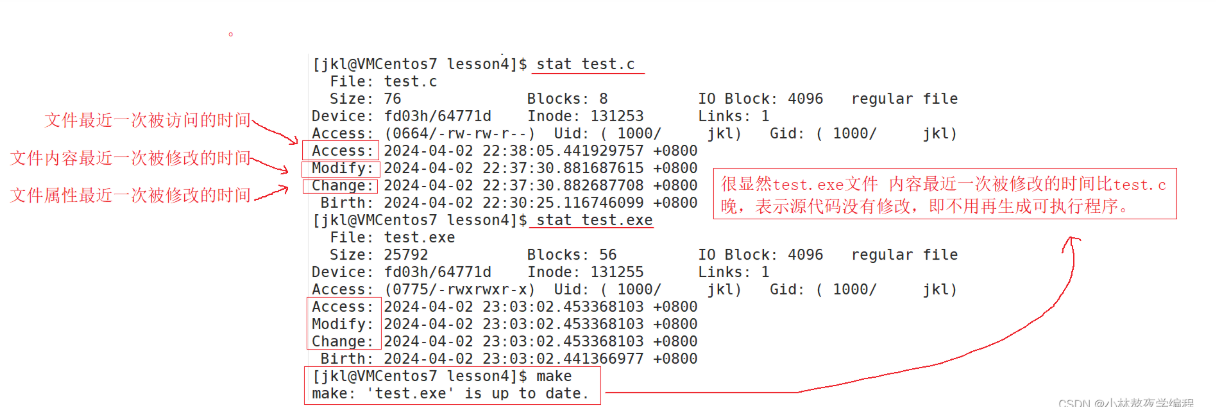

make 会通过文件的时间戳来判断是否需要重新编译。如果源代码文件或依赖文件有修改,make 会重新编译目标文件。否则,它会跳过编译步骤。

[jkl@VMCentos7 lesson4]$ make

make: 'test.exe' is up to date.

1. 为什么再次输入make命令会不让我们继续生成目标文件呢???

因为当有大量的文件的时候,编译执行会消耗大量的时间,为了达到更高的效率,因此当源代码没有改变,makefile就会知道只生成一份可执行程序就可以了。

但是此时就有另外的两个问题了,编译器怎么知道哪个文件是没有改变的源代码???如果我们的目的就是想要输入命令则生成目标文件该怎么办???

2. 编译器怎么知道哪个文件是没有改变的源代码???

对比可执行程序最近修改时间与源文件最近修改时间,谁更新?

编写代码和代码生成的可执行程序的修改时间是不一样的,先写的源代码,后才有的代码生成的可执行程序。因此makefile会通过谁的时间更新,来确定到底要不要重新生成可执行程序。通过stat命令可以看到文件的三个时间。

.

就是 如果 test.c 的 Modify的修改时间新于 test.exe 早,make 会跳过编译,提示:make: 'test.exe' is up to date.

2.2 使用 .PHONY 强制执行目标

有时候,我们希望强制执行某些目标,比如清理编译生成的文件。此时可以使用 .PHONY 来标记这些目标,确保它们总是被执行,即使目标文件存在。

.PHONY: clean

clean:rm -f $(target)

在命令行中执行 make clean 时,make 会执行 clean 目标,删除生成的 test.exe 文件:

[jkl@VMCentos7 lesson4]$ make clean

rm -f test.exe

[jkl@VMCentos7 lesson4]$ ls

makefile test.c

3. Makefile 优化技巧

在实际开发中,Makefile 往往需要进行一些优化,尤其是当项目变得越来越复杂时。下面是一些常见的优化技巧,可以帮助你简化 Makefile,提高构建效率。

3.1 使用自动化变量

Makefile 提供了一些自动化变量,能够让你减少代码的冗余。例如:

-

$@:规则的目标文件。 -

$<:规则中的第一个依赖文件。 -

$^:规则中的所有依赖文件。

优化后的 Makefile 可以变得更加简洁:

target = test.exe

source = test.c$(target): $(source)gcc -o $@ $<.PHONY: clean

clean:rm -f $(target)

3.2 使用变量管理文件

当项目文件较多时,我们可以通过变量来管理源文件、目标文件等,减少冗余代码:

CC = gcc

CFLAGS = -WallSRC = test.c

OBJ = $(SRC:.c=.o)

BIN = test.exe$(BIN): $(OBJ)$(CC) -o $@ $^clean:rm -f $(OBJ) $(BIN)

通过变量管理文件,项目的可维护性和扩展性得到提升。

3.3 自动化生成依赖关系

对于大型项目,可能涉及多个源文件之间的依赖关系。在 Makefile 中,可以通过自动化生成这些依赖关系,避免手动维护。

例如,使用 gcc -M 生成依赖文件:

%.o: %.c$(CC) -M $< > $*.d$(CC) -c $< -o $@

这样,每当源文件发生变化时,make 会自动更新依赖关系。

4. 总结

通过使用 Makefile 和 make 工具,我们可以轻松实现代码编译、链接和清理等任务的自动化,极大提高开发效率。无论是简单的项目,还是复杂的多模块工程,Makefile 都能帮助我们减少手动操作,优化构建过程。

在实际开发中,通过合理利用自动化变量、变量管理、以及生成依赖关系等技巧,我们可以进一步优化 Makefile,提高构建效率和可维护性。掌握 Makefile 的使用,将使你在开发中如鱼得水。