嵌入式芯片中的 SRAM 内容细讲

什么是 RAM?

RAM 指的是“随机存取”,意思是存储单元都可以在相同的时间内被读写,和“顺序访问”(如磁带)相对。

RAM 不等于 DRAM,而是一类统称,包括 SRAM 和 DRAM 两种主要类型。

静态随机存取存储器(SRAM):无需周期性刷新即可保持数据,访问速度快,功耗低,适合存储运行时数据。与 Flash/ROM 区别:Flash 擅长存储代码和常量、掉电不丢失;SRAM 擅长临时数据读写、速度更快但掉电即丢失。

举个例子!!!!STM32F103C8T6 只有 20KB SRAM,你如果搞显示缓存、音频缓存、AI卷积模型、图像中间层数据,瞬间就爆了。

TFT LCD 显示缓存(Frame Buffer)

实时数据缓冲(如ADC/DMA大量采样)

临时变量堆栈、RTOS任务堆栈空间扩展

音频录放缓存、图像缓存

边缘AI推理中间层缓存

通俗易懂来说,使用电脑时,我们会提到内存和内存条的概念,电脑维修的朋友有时候会说加个内存条电脑就不卡了。实际上对于 PC 来说一些情况下卡顿就是电脑同时运行的程序太多了,电脑处理速度变慢的现象。而程序是动态加载到内存中的,一种解决方法就是增加电脑的内存来增加同时可处理的程序的数量。对于单片机也是一样的,高性能有时候需要通过增加大内存来获得。内存是存储器的一种,由于微机架构设计了不同的存储器放置不同的数据,所以我们也简单来了解一下存储器。

| 分类方式 | 类别 | 代表器件示例 |

|---|---|---|

| 按存取方式 | 随机存取存储器 (RAM) | SRAM、DRAM |

| 顺序存取存储器 (SAM) | 磁带 | |

| 按数据保持 | 易失性存储器 | SRAM、DRAM |

| 非易失性存储器 | Mask ROM、EPROM、EEPROM、Flash | |

| 按功能用途 | 主存(内部存储器) | 嵌入式 MCU/SoC 内部 SRAM、DDR DRAM |

| 辅存(外部存储器) | 硬盘(HDD)、固态盘(SSD)、U 盘、SD 卡 | |

| 按存储介质 | 半导体存储器 | SRAM、DRAM、Flash |

| 磁性存储器 | 磁盘、磁带 | |

| 光学存储器 | CD、DVD、Blu‑ray | |

| 机械存储器(软盘等) | 3.5″ 软盘 |

SRAM 在 MCU 中的位置与类型

| 类型 | 作用 | 地址示例(STM32F4) | 特点 |

|---|---|---|---|

| 主 SRAM | 存放堆、栈、全局变量、BSS 等 | 0x2000_0000 – 0x2002_0000 | 容量通常几十 KB – 几百 KB |

| CCM/AXI SRAM | 高速数据交换(DSP、DMA) | 0x1000_0000 – 0x1000_8000 | 无缓存访问、无等待状态、适合 DMA/Motor |

| 备份 SRAM | 低功耗保持 | 0x4000_4000 – 0x4000_8000 | 仅在 VBAT 供电时保持 |

主 SRAM:系统运行的主要工作区;

CCM(Core Coupled Memory):紧耦合于 CPU,访问延迟最低;

备份 SRAM:在待机/掉电模式下由独立供电域维持,用于保存关键数据。

| 项目 | SRAM(静态存储器) | DRAM(动态存储器) |

|---|---|---|

| 英文全称 | Static Random Access Memory | Dynamic Random Access Memory |

| 存储原理 | 使用锁存器(通常由 4~6 个晶体管)保持状态 | 利用 MOS 电容存储电荷,易泄漏,需周期性刷新 |

| 数据保持 | 只要不断电,可永久保存数据 | 需定期刷新电荷,否则数据丢失 |

| 访问速度 | 快,纳秒级 | 较慢,几十纳秒以上 |

| 是否需要刷新 | 否 | 是 |

| 功耗 | 静态功耗高(持续供电),动态功耗较低 | 静态功耗低,但因频繁刷新导致动态功耗高 |

| 集成度/面积 | 面积大、集成度低,单位成本高 | 面积小、集成度高,单位成本低 |

| 价格 | 贵 | 便宜 |

| 稳定性 | 稳定,不易受干扰 | 容易受干扰,需刷新保护 |

| 常见用途 | MCU 内部 RAM、CPU 缓存(L1/L2)、Cache、FPGA Block RAM | PC 主内存、外接内存(SDRAM、DDR 系列)、手机内存 |

| 类型举例 | SRAM、SSRAM(同步 SRAM) | FPRAM、EDO DRAM、SDRAM、DDR、DDR2/3/4/5、RDRAM、SGRAM、WRAM 等 |

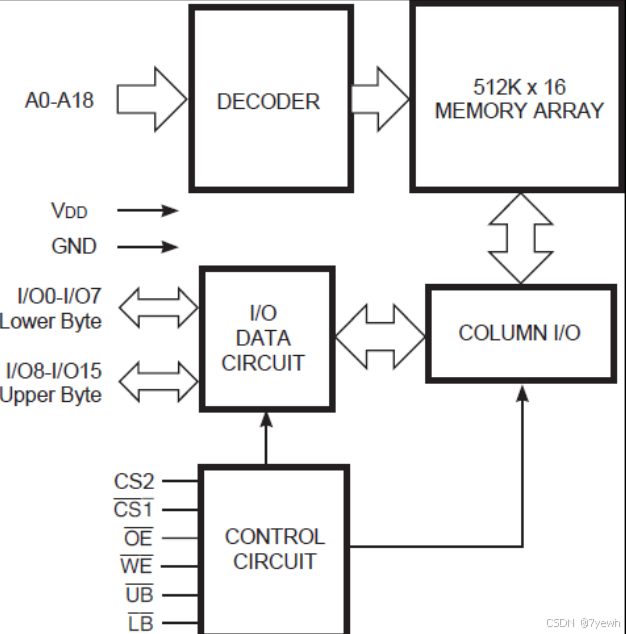

| 信号名称 | 含义 | 详细说明 |

|---|---|---|

A0~A18 | 地址线(共 19 根) | 共 2¹⁹ = 524,288 地址(即 512K 地址空间) |

IO0~IO15 | 数据线(共 16 根) | 每个地址可读写 16 位数据(即 2 字节) |

CS1 | 芯片选择信号(低电平有效) | 必须为低才响应操作 |

CS2 | 芯片选择信号(高电平有效) | 必须为高才响应操作 |

OE | 输出使能(Output Enable) | 为低时,读数据才会输出到 IO 引脚上 |

WE | 写使能(Write Enable) | 为低时执行写操作(和 OE 配合控制读写) |

UB | Upper Byte Enable(高字节控制) | 为低时,写/读数据的 D8~D15 有效 |

LB | Lower Byte Enable(低字节控制) | 为低时,写/读数据的 D0~D7 有效 |

VCC | 电源 | 通常为 3.3V |

GND | 地线 | - |

写操作流程:

1. CS1 = 0,CS2 = 1(片选有效)

2. WE = 0(写有效)

3. OE = 1(关闭输出)

4. 地址 A0~A18 设置好

5. IO0~15 上提供写入数据

6. UB / LB 控制写哪一半数据

读操作流程:

1. CS1 = 0,CS2 = 1(片选有效)

2. WE = 1(写无效)

3. OE = 0(使能输出)

4. 地址 A0~A18 设置好

5. SRAM 把数据放在 IO0~15 上供读取

6. UB / LB 控制读取哪一半数据

ps:字节访问控制(UB/LB 应用场景)如果你只想访问 一个字节(8 位),不必读/写整个 16 位数据,可以使用 UB 或 LB 控制:

UB = 0, LB = 1 → 写/读 高字节(IO8~IO15)

UB = 1, LB = 0 → 写/读 低字节(IO0~IO7)

UB = 0, LB = 0 → 写/读 全 16 位

UB = 1, LB = 1 → 禁止写/读(无操作)

这对嵌入式系统中进行字节级访问很有用,特别是在 ARM Cortex-M MCU 上通过 FMC 总线访问时。

XM8A51216 使用了所谓 “XRAM免刷新技术”,其实本质还是一种 改进型异步 SRAM,其主要特点是:

不需要外部刷新(不像 DRAM)

访问速度高达 10~15ns

内部结构优化,功耗更低、价格更优

可以做到稳定供货,适合国产替代项目

| FSMC 引脚功能 | SRAM 引脚 |

|---|---|

| FSMC_A0~A18 | A0~A18 |

| FSMC_D0~D15 | IO0~IO15 |

| FSMC_NE3 | CS(片选) |

| FSMC_NOE | OE |

| FSMC_NWE | WE |

| FSMC_NBL0 | LB |

| FSMC_NBL1 | UB |

| STM32 FSMC引脚 | SRAM 引脚 |

|---|---|

| FSMC_A0 ~ A18 | A0 ~ A18 |

| FSMC_D0 ~ D15 | IO0 ~ IO15 |

| FSMC_NE3(片选) | CS1(低有效) |

| FSMC_NOE(读使能) | OE |

| FSMC_NWE(写使能) | WE |

| FSMC_NBL0 / NBL1 | LB / UB |

| GND / VCC / VCCO | 电源供电 |

软件初始化步骤(裸机或HAL库)

RCC_AHB3PeriphClockCmd(RCC_AHB3Periph_FSMC, ENABLE);

| 类型 | 举例 |

|---|---|

| SRAM(静态RAM) | IS62WV51216、XM8A51216 等 |

| NOR Flash | 用于存储程序或字库 |

| NAND Flash | 大容量Flash |

| LCD(带并口) | TFT、OLED 等使用 8080 接口的显示屏 |

| 扩展FPGA | 通过 FSMC 扩展高速通信 |

FSMC_NORSRAMInitTypeDef FSMC_InitStructure;

FSMC_NORSRAMTimingInitTypeDef FSMC_Timing;

FSMC_Timing.FSMC_AddressSetupTime = 2;

FSMC_Timing.FSMC_DataSetupTime = 5;

FSMC_Timing.FSMC_ClockDivision = 2;

FSMC_InitStructure.FSMC_Bank = FSMC_Bank1_NORSRAM3;

FSMC_InitStructure.FSMC_DataAddressMux = FSMC_DataAddressMux_Disable;

FSMC_InitStructure.FSMC_MemoryType = FSMC_MemoryType_SRAM;

FSMC_InitStructure.FSMC_MemoryDataWidth = FSMC_MemoryDataWidth_16b;

FSMC_InitStructure.FSMC_BurstAccessMode = FSMC_BurstAccessMode_Disable;

FSMC_InitStructure.FSMC_WriteOperation = FSMC_WriteOperation_Enable;

FSMC_InitStructure.FSMC_ReadWriteTimingStruct = &FSMC_Timing;

FSMC_InitStructure.FSMC_WriteTimingStruct = &FSMC_Timing;

FSMC_NORSRAMInit(&FSMC_InitStructure);

FSMC_NORSRAMCmd(FSMC_Bank1_NORSRAM3, ENABLE);

内存访问(直接指针操作)

#define SRAM_BASE_ADDR ((uint16_t *)0x68000000)

SRAM_BASE_ADDR[0] = 0x1234;

uint16_t val = SRAM_BASE_ADDR[0];

高level的应用,

带缓存机制的数据采集系统(FIFO双缓存切换)

你可以做一个「双缓冲」机制,比如用 FSMC-SRAM 存数据帧,采集和处理同时进行,一边 DMA 填数据,一边 MCU 分析处理。

FSMC+DMA 联动(真正零拷贝)

你可以设置 DMA 从 SRAM 直接输出数据到 LCD(或 DAC),配合 FSMC 写 SRAM 的位置,做到零CPU干预的持续数据流。

做成简易内存管理堆(SRAM 动态 malloc/free)

模拟内存堆,自己写内存分配器,把外扩 SRAM 当作 “扩展堆区”,适合嵌入式 Python、RT-Thread 等系统内存池扩展。

AI 模型中间层缓存

用 FSMC SRAM 放置 CNN 模型运行中间的 feature map,避免 Flash 数据频繁搬运,适合高帧率物体识别、人脸识别。

与 FPGA 联动的共享内存接口

你可以用 FSMC 接到 FPGA,FPGA 的SRAM接口与你 MCU 共享内存,完成高速的数据交互。比如 MCU 控制 + FPGA 实时图像处理的结构。

如果后续要做某个特定场景,比如:显示缓存、AI缓存、动态堆,或者搞点骚操作比如和 FPGA 联动共享内存,我可以帮你进一步设计结构,甚至搞定驱动代码。