电控---SWD协议

SWD协议是烧录调试常用的协议,本文对SWD协议进行了,覆盖物理层、协议层、寄存器结构、信号时序、安全特性、实际应用及最新发展趋势的讲解。

一、物理层架构与信号特性

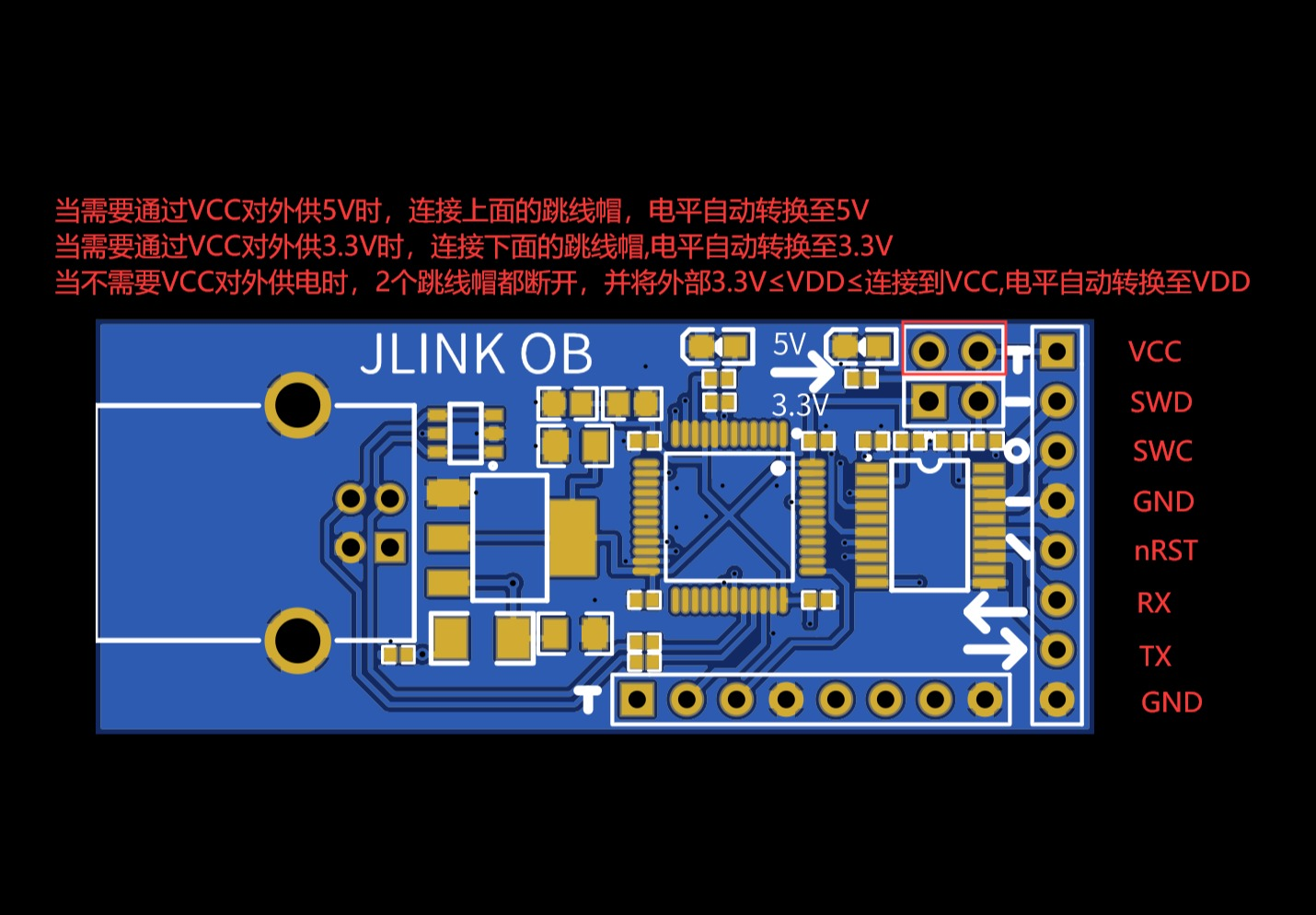

1. 引脚定义与电气规范

- 核心引脚:

- SWDIO(双向数据线):开漏输出,需外部4.7kΩ上拉电阻(典型值),支持3.3V/1.8V电平自适应。

- SWCLK(时钟线):由主机提供,频率范围0.1MHz至100MHz(如ADI ICE-2000支持46MHz,部分芯片支持100MHz)。

- 可选引脚:

- nRST(复位):用于强制芯片复位,部分调试器(如ST-Link)支持硬件复位。

- SWO(串行线输出):用于实时跟踪调试(如ARM CoreSight的ITM/ETM),需独立引脚。

2. 信号传输机制

- 差分编码:每个时钟周期传输两位数据(上升沿和下降沿各一位),理论带宽是JTAG的两倍。

- 半双工模式:同一时刻只能单向传输,通过转向周期(Turnaround)切换方向,延迟约10-20ns。

- 同步机制:SWCLK的上升沿驱动数据,下降沿采样数据,确保信号完整性。

3. 电路设计要点

- 上拉电阻:SWDIO和SWCLK需接4.7kΩ上拉电阻至VDD,容差≤5%。

- 信号完整性:

- 走线长度≤5cm,避免高速信号反射。

- 差分对布局,间距≥100mil。

- 靠近芯片端串联30-100Ω电阻(如STM32推荐33Ω),抑制EMI。

- 去耦电容:在SWD接口附近放置100nF电容,降低电源噪声。

二、协议层详解

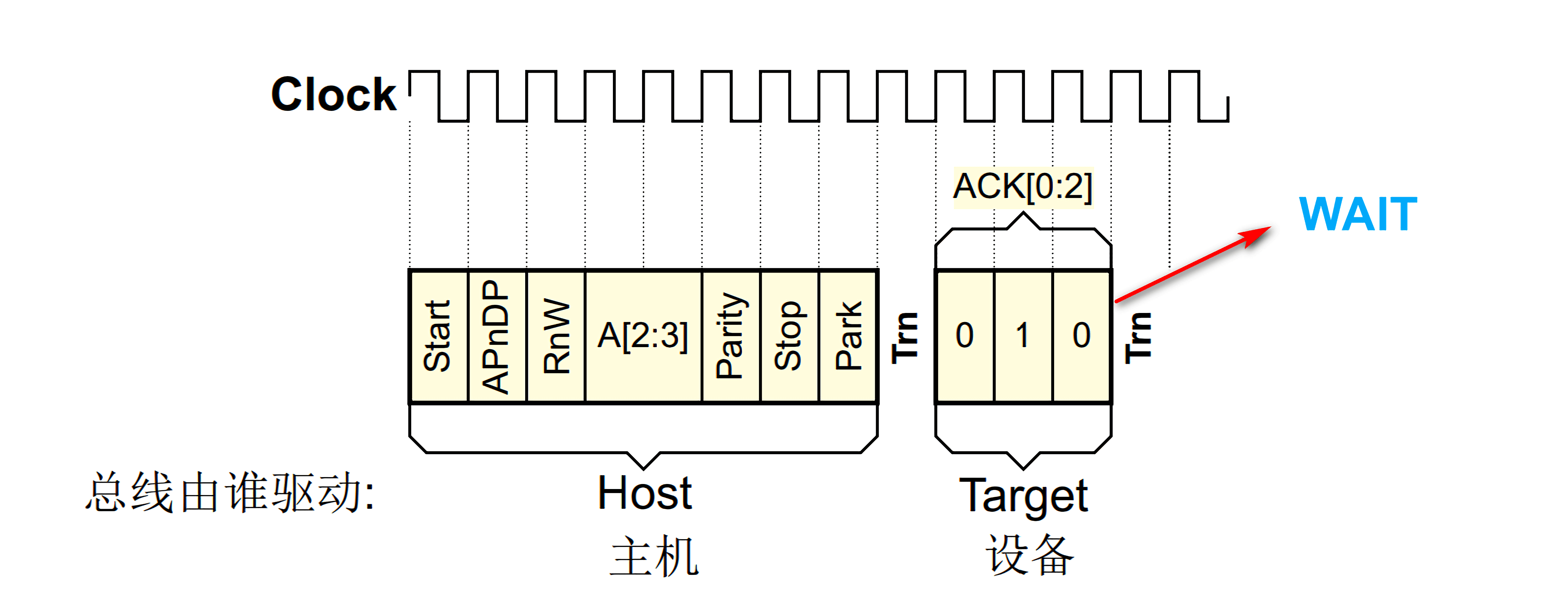

1. 数据包格式

-

请求包(Host→Target):

[Start(1)] [APnDP(1)] [RnW(1)] [Addr(2)] [Parity(1)] [Stop(0)] [Park(1)]- Start:固定为1,标识传输开始。

- APnDP:0表示访问调试端口(DP),1表示访问应用端口(AP)。

- RnW:0为写操作,1为读操作。

- Addr:寄存器地址(DP为2位,AP为4位)。

- Parity:校验位(APnDP + RnW + Addr的奇校验)。

- Stop:固定为0。

- Park:固定为1,释放SWDIO控制权。

-

响应包(Target→Host):

[ACK(3)] [Data(32)] [Parity(1)]- ACK:三位状态码(100=成功,010=等待,001=失败)。

- Data:32位数据(读操作时返回)。

- Parity:数据校验位。

2. 寄存器访问流程

- 调试端口(DP):

- IDCODE:芯片唯一标识(如0x0BB11477表示STM32F103)。

- ABORT:中止当前事务,处理错误状态。

- CTRL_STAT:控制调试端口状态,如使能时钟。

- RDBUFF:存储AP返回的数据。

- 应用端口(AP):

- CSW:配置访问内存的大小(8/16/32位)。

- TAR:指定内存地址。

- DRW:读写数据寄存器。

- IDR:AP模块标识。

3. 初始化流程

- Line Reset:主机发送至少50个高电平脉冲,强制目标设备复位。

- 协议切换:发送特定序列(如0x79、0xE7)将JTAG模式切换为SWD。

- 读取IDCODE:验证设备存在并获取型号信息。

- 解锁AP:通过DP寄存器使能AP访问权限。

三、信号时序与错误处理

1. 典型时序阶段

- 请求阶段:主机发送8位命令(Start + APnDP + RnW + Addr + Parity + Stop + Park)。

- ACK阶段:目标返回3位ACK码,可能包含转向周期(Trn)。

- 数据阶段:传输32位数据(写操作由主机发送,读操作由目标返回)。

- 校验阶段:传输1位奇偶校验位。

2. 错误处理机制

- FAULT响应(001):目标设备返回错误,主机需重新发送命令或检查硬件连接。

- WAIT响应(010):目标未准备好,主机延迟后重试。

- 超时机制:主机在指定时间内未收到响应,触发重试或报错。

3. 转向周期(Trn)

- 作用:在读写切换时插入空闲周期,确保信号稳定。

- 时长:1-2个时钟周期,由目标设备的TURNROUND寄存器配置。

四、高级功能与安全特性

1. 实时跟踪(SWO)

- 原理:通过SWO引脚输出实时调试信息(如指令执行流、变量值),依赖ARM CoreSight的ITM/ETM模块。

- 配置步骤:

- 使能ITM模块(SCB->DEMCR |= SCB_DEMCR_TRCENA_Msk)。

- 配置SWO引脚(如STM32的PA3)。

- 使用调试工具(如J-Link SWO Viewer)捕获数据。

2. 安全增强

- 熔丝位禁用:通过芯片熔丝位(如ARM的SECURE_FUSE)永久关闭SWD接口。

- 加密传输:部分调试工具(如J-Link)支持AES加密通信,保护固件安全。

- 存储保护:

- RDP(读保护):全局Flash读保护,防止逆向工程。

- WRP(写保护):禁止擦写指定区域。

- PCROP(专有代码保护):限制代码读取和修改。

3. 低功耗设计

- 时钟门控:空闲时关闭SWCLK。

- 动态电压调整:通过寄存器配置动态调整工作电压。

- 休眠模式兼容:设备进入休眠(如STM32的Stop模式)时,SWD仍可唤醒并通信。

五、与JTAG的深度对比

| 特性 | SWD | JTAG |

|---|---|---|

| 引脚数量 | 2根(SWDIO+SWCLK) | 4-5根(TCK/TMS/TDI/TDO/TRST) |

| 速度 | 最高100MHz | 最高50MHz |

| 功耗 | 低(优化时钟管理) | 高(持续时钟) |

| 功能 | 调试、编程 | 调试、边界扫描测试 |

| 适用场景 | 引脚受限的嵌入式设备 | 复杂系统级测试 |

六、实际应用与工具链

1. 调试器支持

- 主流工具:Segger J-Link、ST-Link、OpenOCD(开源)。

- 协议分析:逻辑分析仪(如Saleae)可捕获SWD信号进行调试。

2. IDE集成

- Keil MDK:默认优先使用SWD,支持硬件断点、内存映射。

- IAR Embedded Workbench:通过配置文件切换协议。

- ARM Development Studio:支持实时跟踪和性能分析。

3. 典型代码示例

// STM32F103配置SWD

RCC->APB2ENR |= RCC_APB2ENR_AFIOEN; // 使能AFIO时钟

AFIO->MAPR &= ~AFIO_MAPR_SWJ_CFG; // 禁用JTAG,启用SWD

AFIO->MAPR |= AFIO_MAPR_SWJ_CFG_JTAGDISABLE;GPIO_InitTypeDef GPIO_InitStructure;

GPIO_InitStructure.GPIO_Pin = GPIO_Pin_13 | GPIO_Pin_14; // PA13(SWDIO), PA14(SWCLK)

GPIO_InitStructure.GPIO_Mode = GPIO_Mode_AF_PP;

GPIO_InitStructure.GPIO_Speed = GPIO_Speed_50MHz;

GPIO_Init(GPIOA, &GPIO_InitStructure);

七、发展趋势与前沿技术

- 更高频率支持:部分调试器(如J-Link Ultra+)支持150MHz SWD,提升下载速度。

- USB-C集成:SWD over USB-C成为趋势,简化连接(如J-Link Edu Mini)。

- 硬件级加密:如ARMv9架构支持调试接口加密,防止未授权访问。

- 与其他协议融合:SWD与UART、SPI结合,实现多功能调试(如SWO+SWD复用)。

八、注意事项与常见问题

- 硬件设计:

- 确保SWDIO和SWCLK走线短且远离高频信号。

- 外部上拉电阻取值4.7kΩ,确保信号完整性。

- 软件配置:

- 初始化时需正确设置AFIO_MAPR寄存器以切换协议模式。

- 进入低功耗模式前,关闭非必要外设时钟。

- 兼容性:

- 部分芯片(如STM32F103)默认同时启用JTAG和SWD,需通过寄存器禁用JTAG以释放引脚。

九、总结

SWD协议凭借其引脚少、速度快、低功耗等优势,已成为ARM架构微控制器调试的首选方案。其核心设计包括差分编码、半双工通信、寄存器分层访问等,结合实时跟踪、安全加密和低功耗优化,满足嵌入式开发的多样化需求。在实际应用中,需结合硬件设计、协议配置及工具链优化,以充分发挥其性能。对于复杂系统或需要边界扫描测试的场景,JTAG仍是更合适的选择。未来,SWD将进一步向高速化、安全化和多功能化发展,成为嵌入式调试领域的主流标准。