【FPGA开发】Vivado开发中的LUTRAM占用LUT资源吗

LUTRAM在Vivado资源报告中的解释

LUTRAM的本质与实现原理:

LUTRAM不是一种独立的物理资源,而是LUT(Look-Up Table)的一种特殊使用方式。在Xilinx FPGA架构中,部分LUT单元可以被配置为小型分布式RAM(也称为分布式存储器),这就是LUTRAM。

资源共享关系:

- LUTRAM使用的是与普通逻辑相同的LUT物理结构,但配置方式不同

- 不是所有LUT都能用作LUTRAM,只有特定子集可以这样配置

- 当一个LUT被用作LUTRAM时,它就不能同时用于普通组合逻辑

报告分开显示的原因:

Vivado将LUTRAM单独列出是为了帮助设计者了解LUT资源的分配情况,以便:

- 清楚地看到有多少LUT用于存储而非逻辑功能

- 在资源受限时进行优化决策(例如,考虑使用BRAM替代LUTRAM)

- 更好地分析设计中存储资源的分布

设计优化考虑:

如果你的设计接近LUT资源上限,可以考虑:

- 将部分LUTRAM实现转移到BRAM实现

- 分析是否有效率较低的存储器实现方式

- 检查小型RAM是否有更优的实现策略

总结来说,LUTRAM是LUT的一种功能配置,在报告中单独列出是为了更清晰地展示资源使用情况,而不是表示它们是完全独立的物理资源。

BUFG(全局时钟缓冲器)

基本定义:

BUFG是Global Clock Buffer(全局时钟缓冲器)的缩写,是FPGA中专用于时钟信号分发的资源。

主要功能:

- 将时钟信号分配到FPGA的大范围区域,确保低偏斜(低skew)分布

- 驱动大量逻辑单元,能够覆盖整个器件或大部分区域

- 提供低时钟延迟和高扇出能力

在设计中的重要性:

- 用于驱动关键时钟路径和高扇出网络

- 确保时钟树的平衡和同步

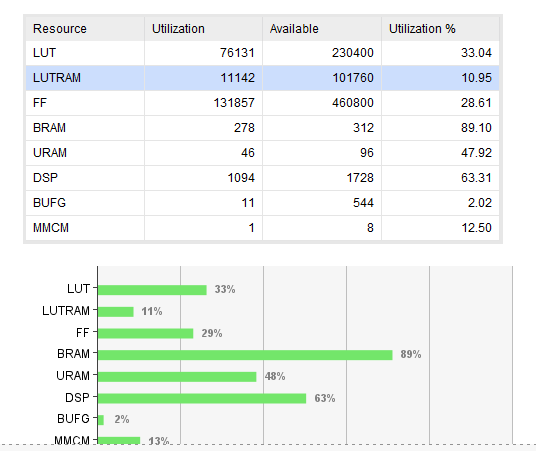

- 有限资源(在你的设计中总共有544个,已使用11个)

MMCM(混合模式时钟管理器)

基本定义:

MMCM是Mixed-Mode Clock Manager的缩写,是一种高级时钟合成和管理单元。

主要功能:

- 频率合成:从输入时钟生成多个不同频率的输出时钟

- 相位调整:精确控制时钟相位关系

- 动态重配置:运行时可调整时钟参数

- 抖动过滤:通过内部电路减少时钟信号抖动

技术特性:

- 包含数字锁相环(DLL)和锁相环(PLL)电路

- 支持分频和倍频功能

- 提供精确的时钟延迟补偿

- 支持多种输入/输出时钟关系

应用场景:

- 接口时序要求严格的高速接口(如DDR内存)

- 需要多个相关但频率不同的时钟域

- 需要精确相位控制的应用

- 跨时钟域设计

资源限制:

在你的设计中,总共有8个MMCM单元,目前使用了1个(12.5%)。

在FPGA设计中的关系

MMCM生成时钟信号后,通常会通过BUFG将这些时钟分发到FPGA的不同区域。这两种资源协同工作,构成了FPGA的时钟网络基础设施,对于确保设计的时序性能至关重要。