ARM架构的微控制器总线矩阵

在 ARM 架构的微控制器(MCU)中,总线矩阵(Bus Matrix) 是总线系统的核心互连结构,负责协调多个主设备(如 CPU、DMA、以太网控制器等)对多个从设备(如 Flash、SRAM、外设等)的并发访问。其设计目标是提升系统吞吐量、降低访问冲突,并支持并行操作。

—

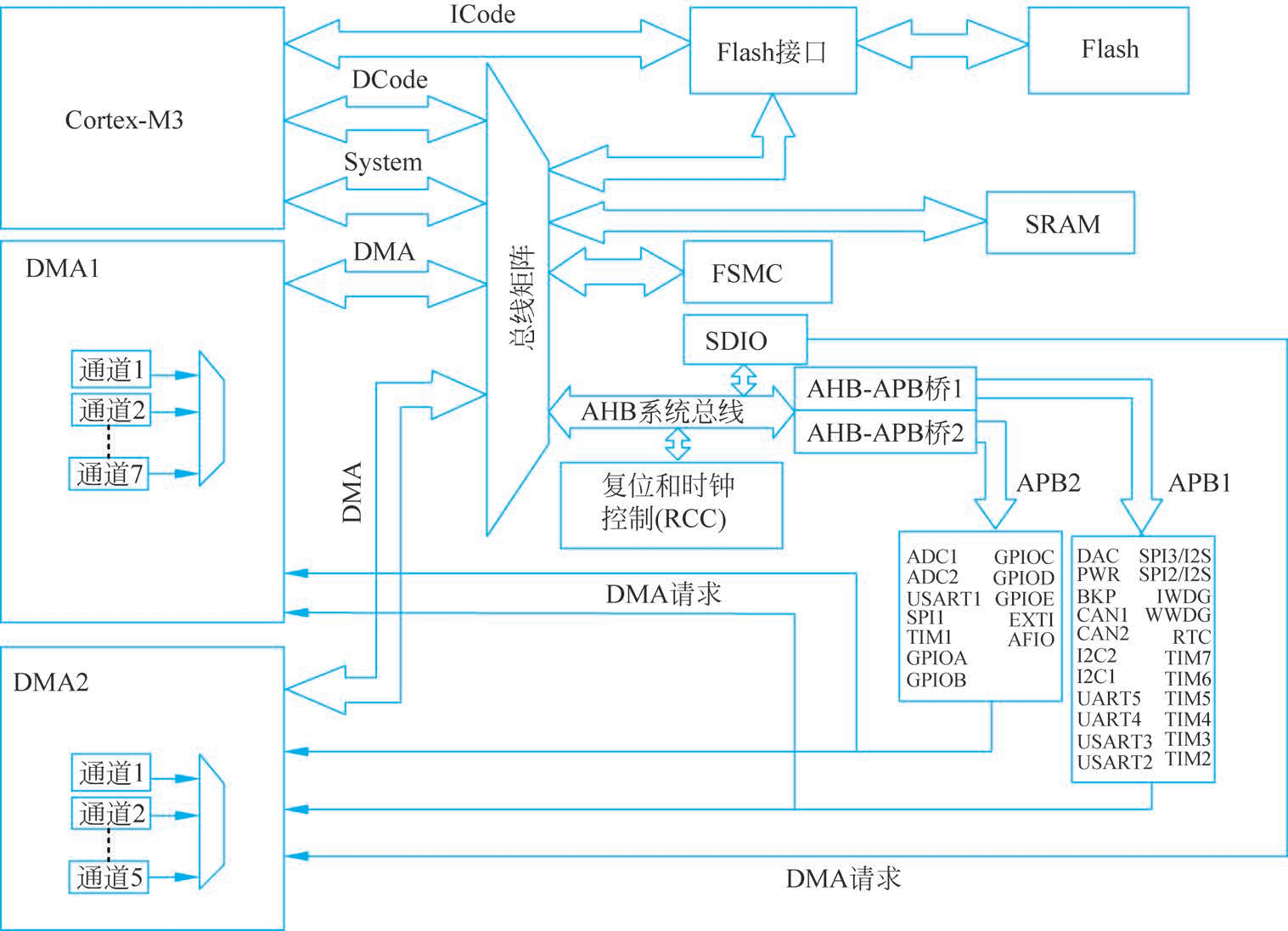

STM32F103系统架构图

总线矩阵的核心功能

- 多主设备并发访问

允许多个主设备同时访问不同的从设备(例如:CPU 读取 Flash 时,DMA 可以同时写 SRAM)。 - 优先级仲裁

当多个主设备请求同一从设备时,仲裁器根据预设优先级分配访问权。 - 地址解码与路由

将主设备的请求路由到目标从设备(如地址范围决定访问 Flash 还是外设)。 - 低延迟与高带宽

通过并行路径减少总线争用,提升实时性。

总线矩阵的典型结构

1. 主端口(Master Ports)

连接需要发起总线操作的主设备,例如:

- CPU 核心(Cortex-M)

- DMA 控制器

- 高速外设(如以太网 MAC、USB 控制器)

2. 从端口(Slave Ports)

连接被访问的从设备,例如:

- Flash 控制器

- SRAM 控制器

- AHB-APB 桥(连接低速外设)

- 外设寄存器

3. 仲裁器(Arbiter)

- 当多个主设备请求同一从设备时,决定访问顺序。

- 仲裁策略可以是固定优先级(如 DMA 优先级高于 CPU)或轮询(Round-Robin)。

4. 地址解码器(Decoder)

- 解析主设备的地址请求,确定目标从设备。

- 例如:地址

0x0000_0000–0x1FFF_FFFF映射到 Flash,0x2000_0000–0x3FFF_FFFF映射到 SRAM。

5. 数据路径(Data Path)

- 提供物理连接通道,支持多路独立传输路径。

总线矩阵 vs. 传统共享总线

| 特性 | 总线矩阵 | 传统共享总线 |

|---|---|---|

| 并发性 | 多主设备同时访问不同从设备 | 单主设备独占总线 |

| 效率 | 高吞吐量,低延迟 | 易出现总线争用,效率受限 |

| 复杂度 | 高(需要路由和仲裁逻辑) | 低 |

| 适用场景 | 多核/多主设备系统 | 简单单主设备系统 |

总线矩阵的典型应用场景

- CPU 与 DMA 并行操作

- CPU 从 Flash 读取代码时,DMA 可以将 ADC 采集的数据写入 SRAM。

- 多外设并发访问

- 以太网控制器发送数据包时,USB 控制器可以同时接收数据。

- 实时性要求高的系统

- 避免因总线阻塞导致关键任务(如中断响应)延迟。

总线矩阵的实现示例(以 Cortex-M7 为例)

主设备端:├── Cortex-M7 核心(通过 AHB 或 AXI 总线)├── DMA1 控制器├── DMA2 控制器└── 以太网 MAC从设备端:├── Flash 控制器(0x0800_0000)├── SRAM1(0x2000_0000)├── SRAM2(0x2001_0000)├── AHB-APB 桥(连接 APB 外设)└── 外部存储器接口(FSMC/FMC)总线矩阵逻辑:└── 根据地址和仲裁规则,动态分配主设备到从设备的路径。

总线矩阵的设计考量

- 时钟域

- 主设备和从设备可能运行在不同时钟频率,需同步逻辑。

- 主设备数量

- 总线矩阵的复杂度随主设备数量增加而显著上升。

- 延迟与吞吐量

- 高频系统中需优化数据路径宽度(如 32-bit/64-bit)。

- 低功耗模式

- 空闲时关闭未使用的总线段以降低功耗。

总线矩阵的优势

- 提升系统性能:通过并行操作最大化带宽利用率。

- 增强实时性:避免关键任务因总线阻塞而延迟。

- 简化系统设计:标准化接口(如 AHB/AXI)便于集成第三方 IP 核。

总结

总线矩阵是 ARM MCU 实现高效多主设备协同的核心机制,尤其在高性能 Cortex-M7/M33 或 Cortex-A 系列中广泛应用。其灵活的路由和仲裁能力,使得复杂嵌入式系统(如实时控制系统、物联网网关)能够兼顾性能与实时性。