利用quartus的DDS函数信号发生器设计

一、功能要求

采用数字频率合成(Direct Digital FrequencySynthesis,简称DDS)设计制作一个波形发生器,仿真后,在DE2-115开发板上实践。

要求:

1、利用DDS技术合成正弦波和方波;

2、输出信号的频率范围为10Hz~5MHz,最小频率分辨率小于1kHz;

3、使用嵌入式逻辑分析仪SignalTap II实时测试输出波形的离散数据。

二、设计分析

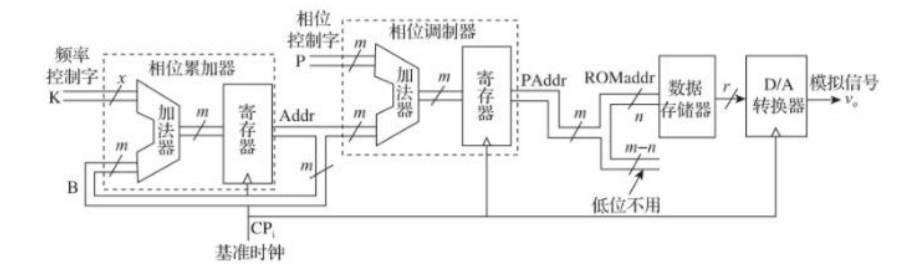

在FPGA中,常用所示框图实现DDS。

其中,m为地址加法器的数据宽度,其大小取决于基准时钟频率和所需步进精度。ROMaddr为n位存储器地址,n取决于波形样本个数。r为存储器输出数据的宽度。地址计数器也称为相位累加器,由地址加法器和地址寄存器组成。加法器有两个数据输入端:一个输入端B与地址寄存器的输出相连;另一个输入端为相位增量K,因为K是决定DDS输出频率的参量,所以被称为频率数据或频率控制字(Frequency Control Word, FCW),存放K的寄存器称为频率控制寄存器。频率控制字K是一个二进制数据,K+B(B的初值为0)就是相位累加器的输出Addr,相位控制字P用来调节相对于相位累加器输出相位的一个固定增量,对于一路信号来说没有任何意义,不过对于多路信号来说,可以通过相位控制字来调节多路信号的相位差。

存储器地址ROMaddr截取的是PAddr的高n位,其变化速度取决于K的大小,从而实现了跳跃读数。当相位累加器为最大值时,再来一个时钟脉冲,其输出地址数据出现溢出,自动地从0开始重复先前的过程,这样就可以实现波形的连续输出。因此通过改变K值来调节输出频率。

【1】相位累加器的设计

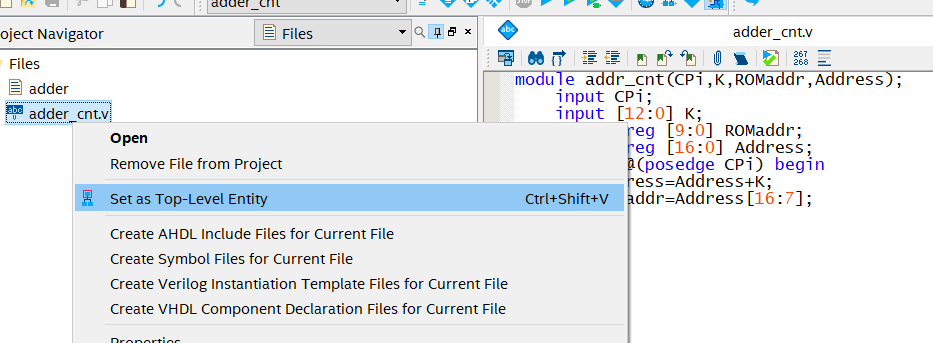

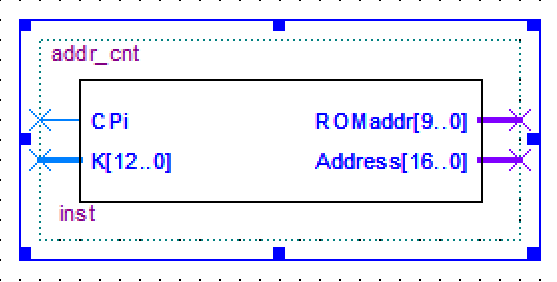

Quartus新建工程,新建.v文件取名addr_cnt.v,代码如下:

module addr_cnt(CPi,K,ROMaddr,Address);input CPi;input [12:0] K;output reg [9:0] ROMaddr;output reg [16:0] Address;always @(posedge CPi) beginAddress=Address+K;ROMaddr=Address[16:7];end

endmodule

保存后,右键点击文件Set as Top Level Entity,编译运行成功后再次右键单击,选择Create Symbol Files for Current File

Quartus打开.bsf文件,生成该模块的符号如下:

【2】波形存储器ROM

1、方波模块

代码:

module squwave(CPi,RSTn,Address,Qsquare);input CPi;input RSTn;input [16:0] Address;output reg [11:0] Qsquare;always @(posedge CPi)if (!RSTn)Qsquare=12'h000; else beginif(Address<=17'h0FFFF)Qsquare=12'hFFF;else Qsquare=12'h000;end

endmodule

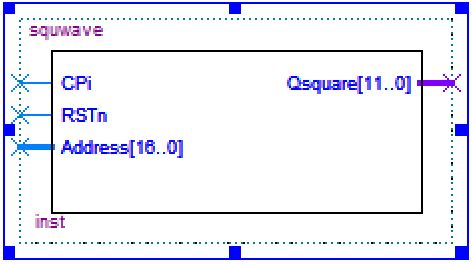

模块符号:

2、正弦波形存储器

这个比较复杂,需要用IP核调用ROM存储。但是直接IP核生成ROM并更改存储数据太麻烦了,我们可以编写一个C语言程序,生成存储器的初始化文件Sine1024.mif。

C语言程序如下:

/*myMIF.c*/

#include <stdio.h>

#include <math.h>

#define PI 3.141592

#define DEPTH 1024

#define WIDTH 12

int main(void)

{int n,temp;float v;FILE *fp;fp=fopen("Sine1024.mif","w+");if(NULL==fp)printf("Can not creat file!\r\n");else{printf("File created successfully!\n");fprintf(fp,"DEPTH=%d;\n",DEPTH);fprintf(fp,"WIDTH=%d;\n",WIDTH);fprintf(fp,"ADDRESS_RADIX=HEX;\n");fprintf(fp,"DATA_RADIX=HEX;\n");fprintf(fp,"CONTENT\n");fprintf(fp,"BEGIN\n");for(n=0;n<DEPTH;n++){v=sin(2*PI*n/DEPTH);temp=(int)((v+1)*4095/2);fprintf(fp,"%04x : %03x;\n",n,temp);}fprintf(fp,"END;\n");fclose(fp);}}

编译运行该C程序后,可以在文件所在目录下看到一个myMIF.exe文件,双击即可生成Sine1024.mif文件。

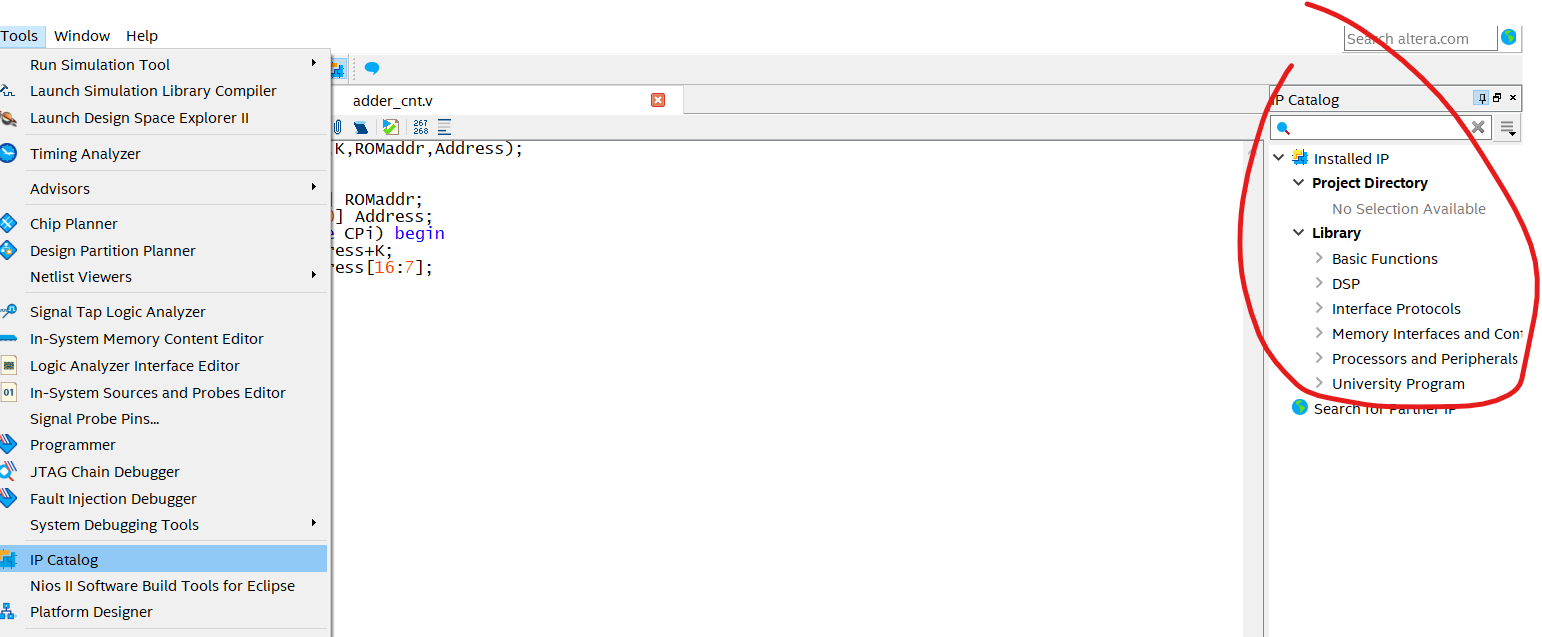

使用Quartus调用LPM_ROM定制正弦波形存储器:点击Tools->IP Catalog

在IP Catalog界面搜索栏中输入ROM,双击ROM 1-PORT(如果点击没有反应那你可以看看右边QWQ)

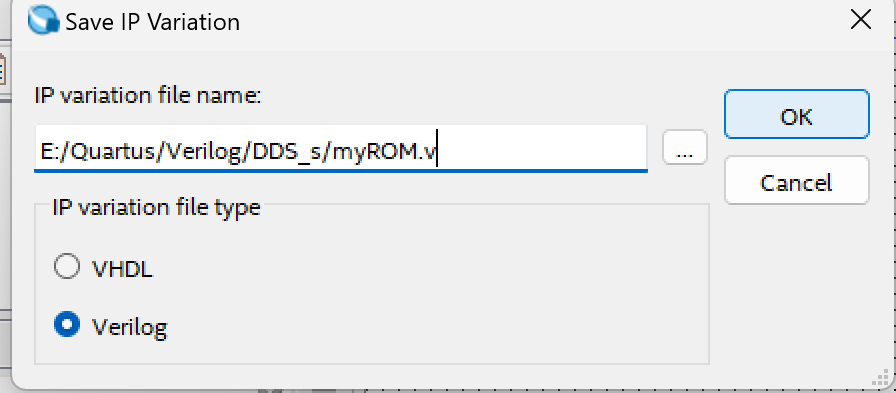

命名为SineROM.v,点击OK

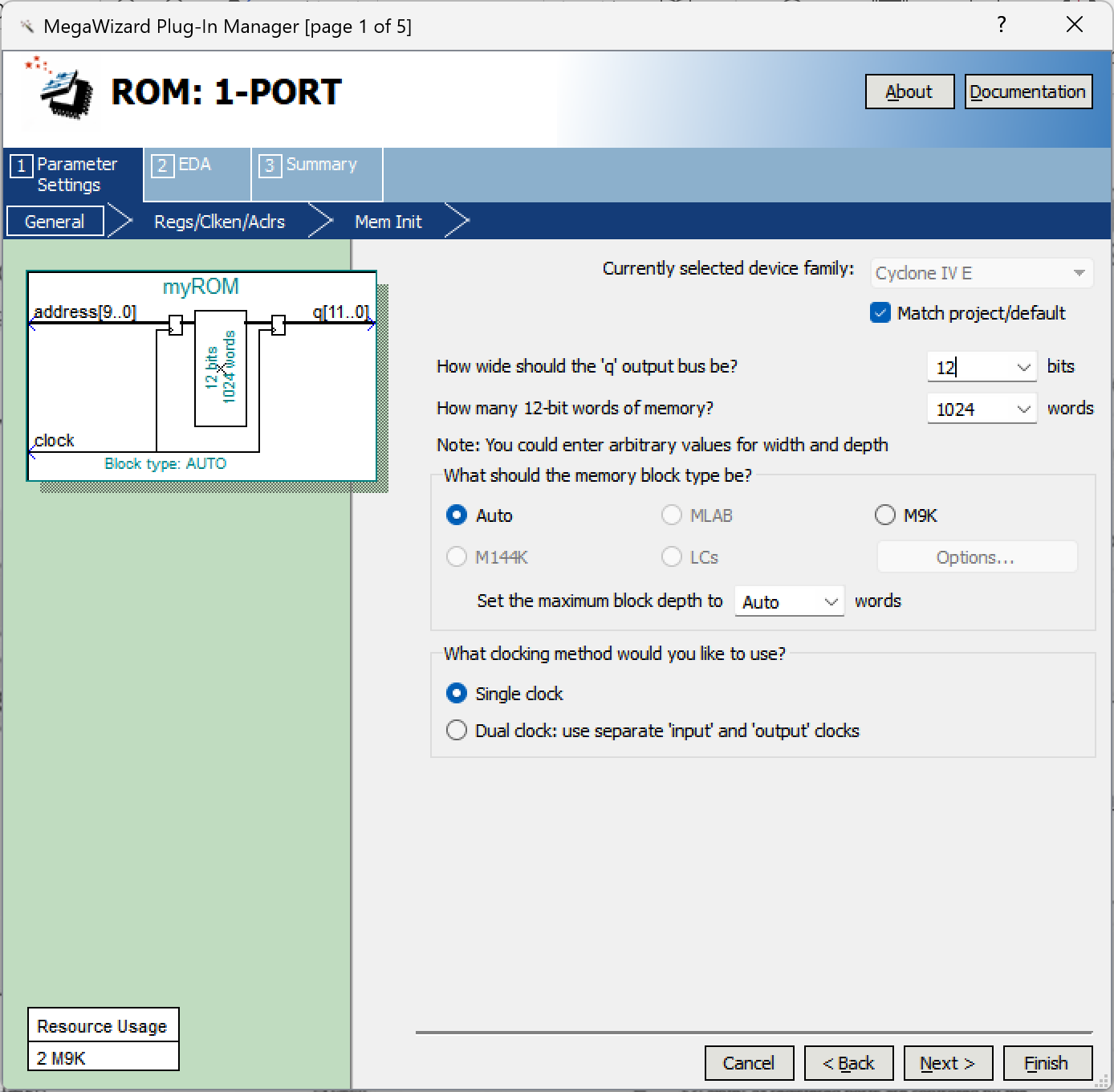

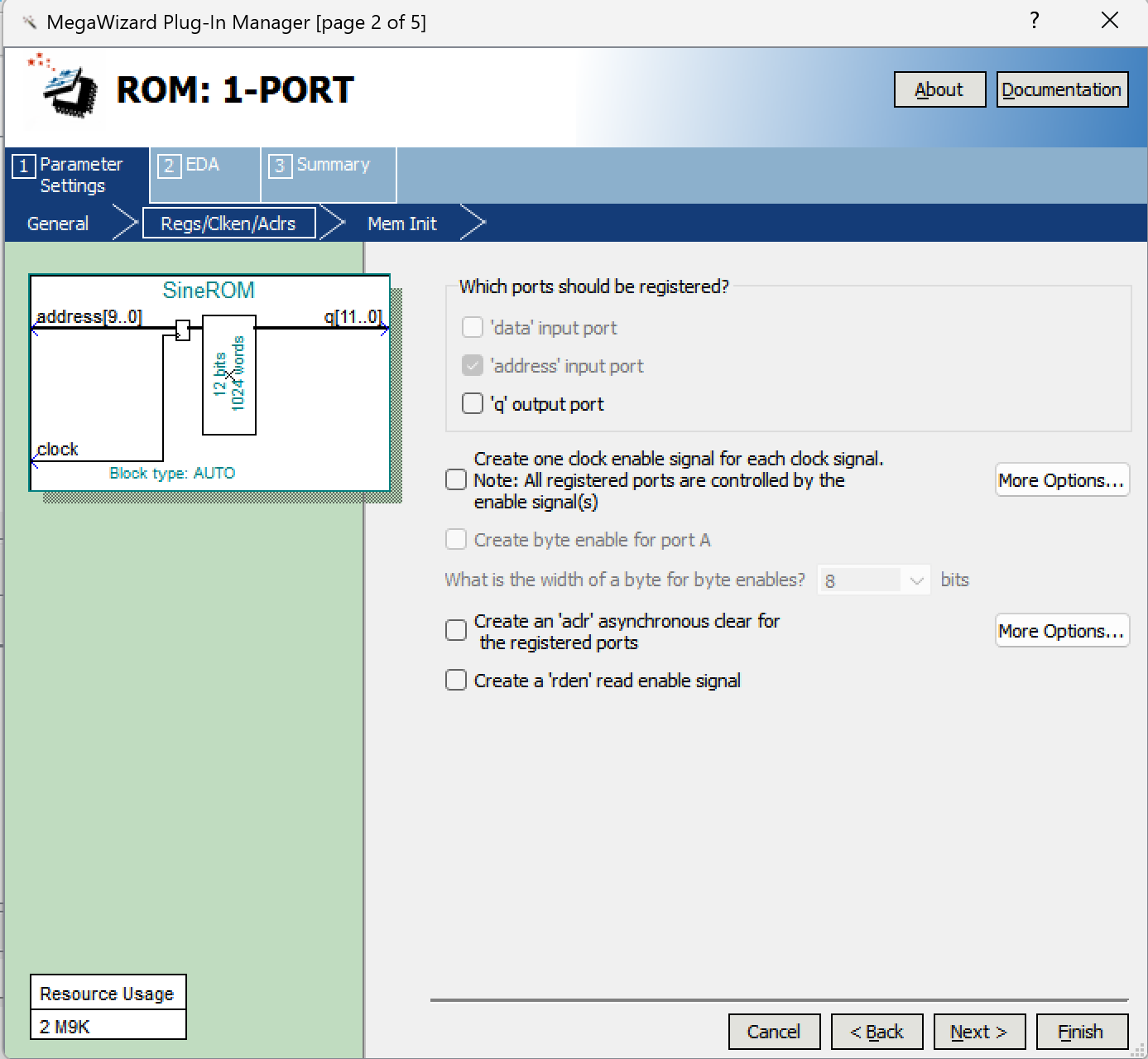

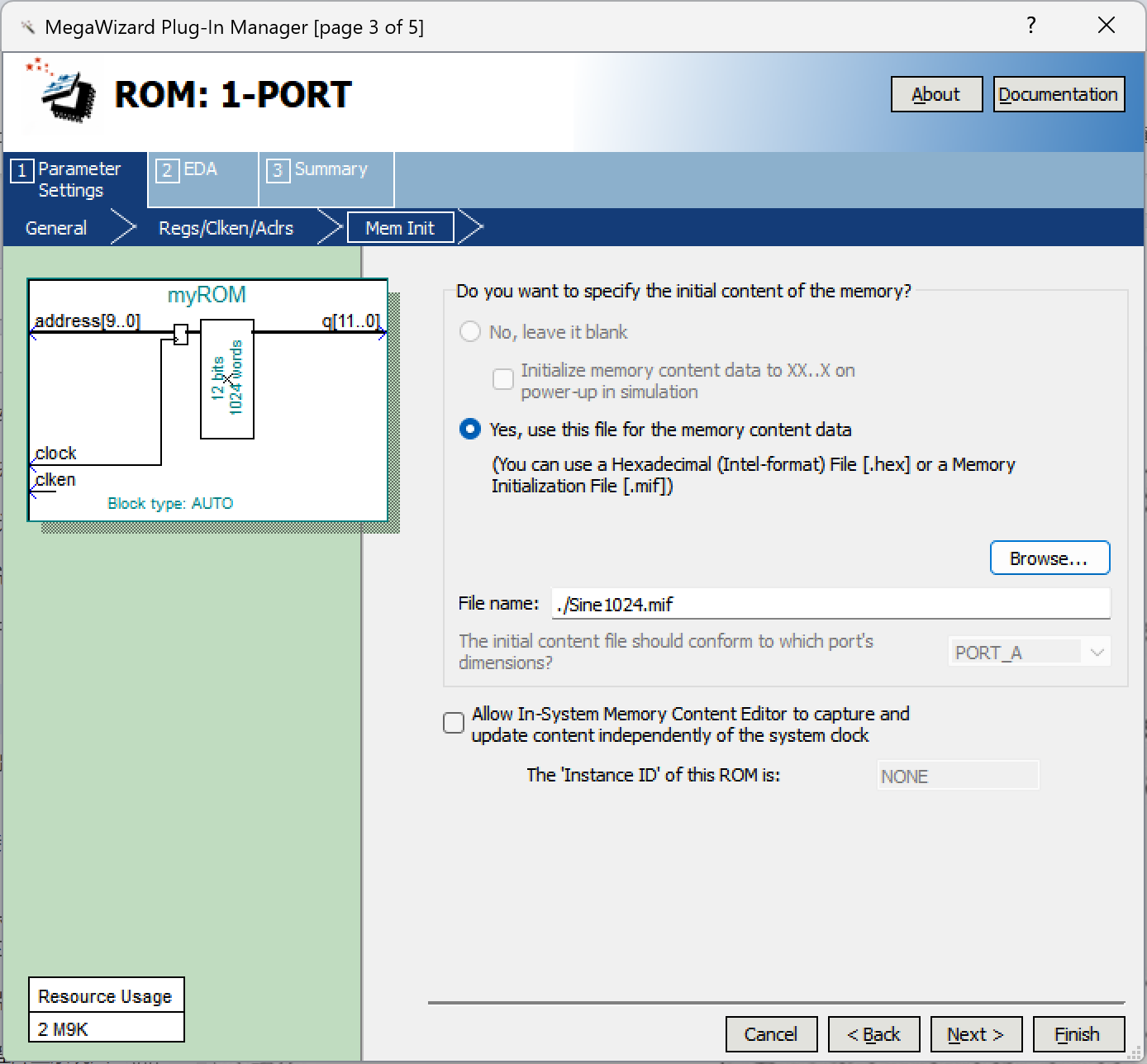

之后的除下图所示界面需要特别设置以外,其它点击Next跳过即可。

至此,ROM配置完成了。

【3】锁相环倍频电路

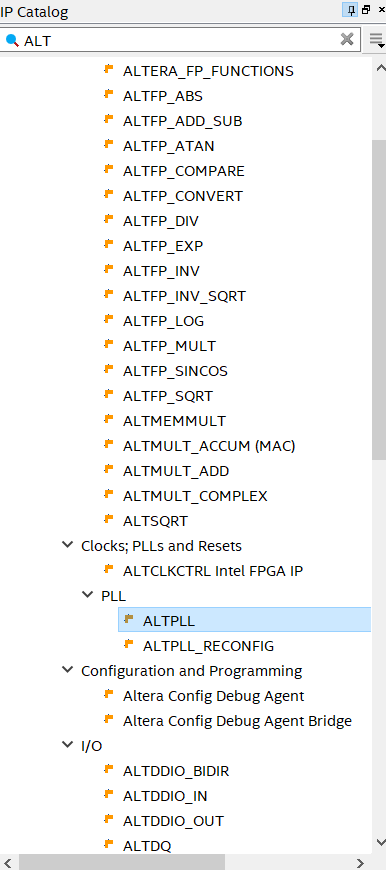

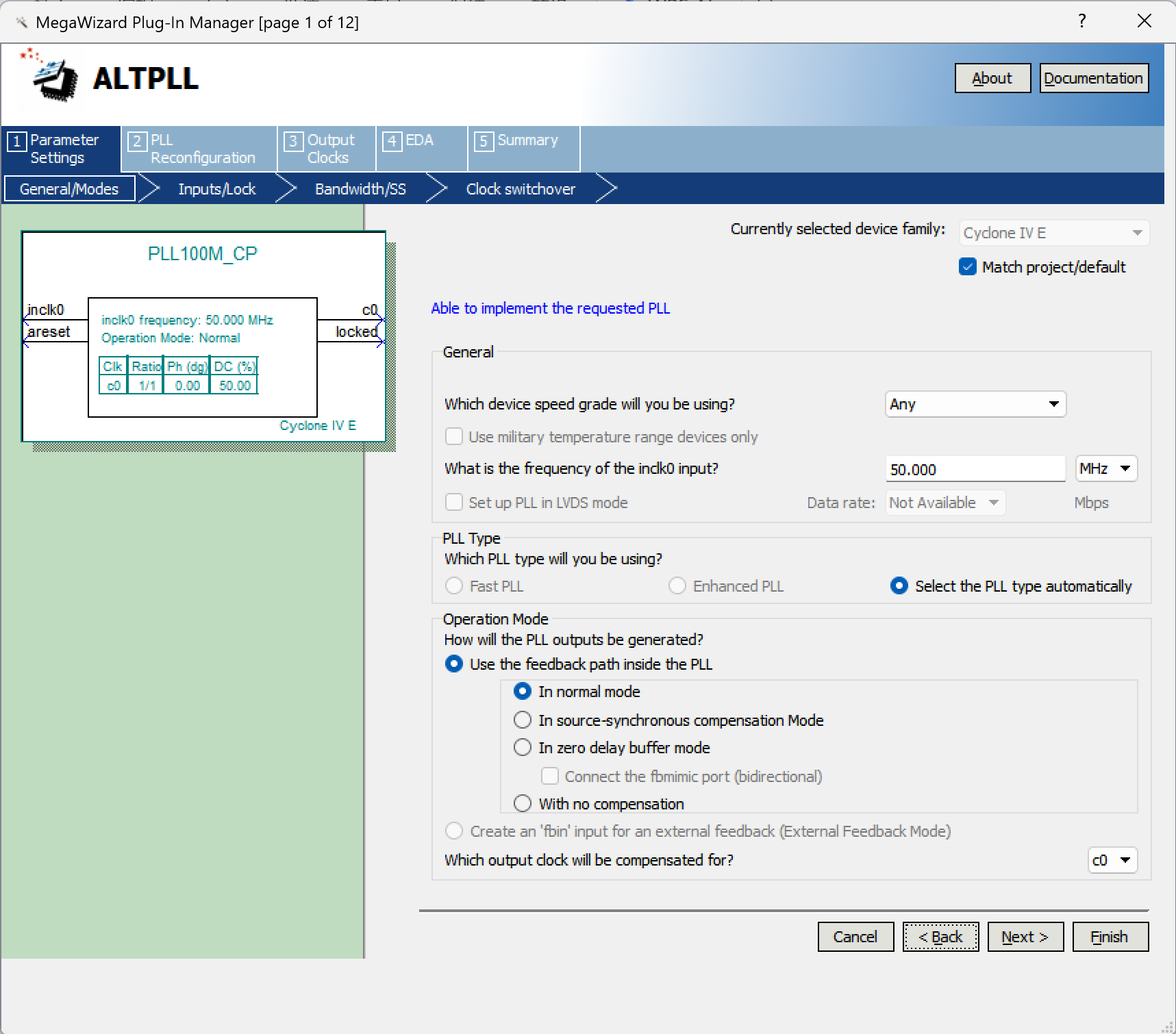

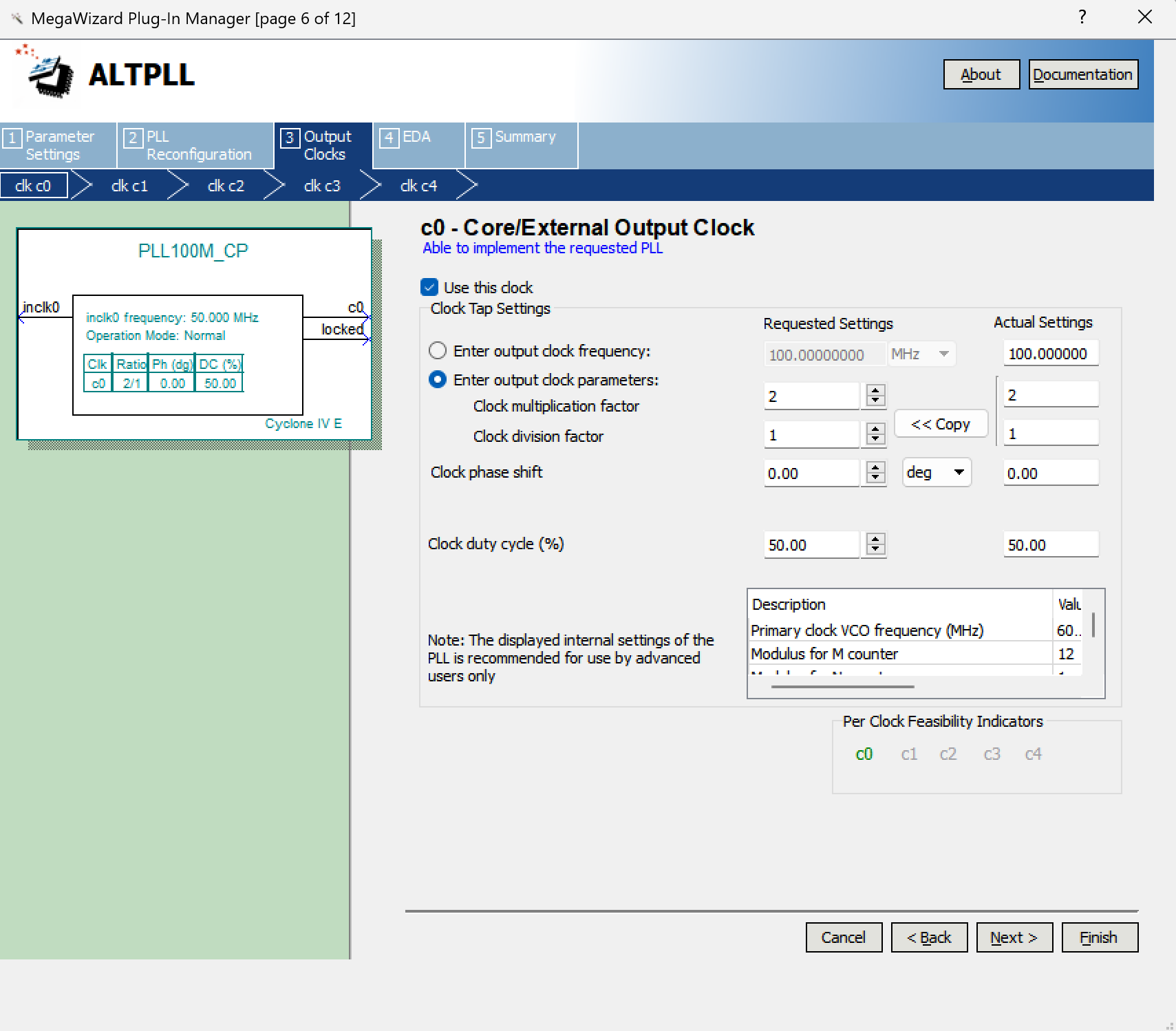

在IP Catalog搜索栏输入APTPLL,双击图示蓝框选项。

除如下所示图片需要更改一些设置外,其余界面next掉就好。

【4】顶层电路设计

将这个代码设为顶层文件,编译。

module DDS_top (CLOCK_50,RSTn,WaveSel,K,

WaveValue,LEDG,CLOCK_100);input CLOCK_50;input RSTn;input [1:0] WaveSel;input [12:0] K;output reg [11:0] WaveValue;wire [9:0] ROMaddr/* synthesis keep */;wire [16:0] Address;wire [11:0] Qsine,Qsquare;output [0:0] LEDG;output CLOCK_100;wire CPi=CLOCK_100;PLL100M_CP PLL100M_CP_inst(.inclk0(CLOCK_50),.c0(CLOCK_100),.locked(LEDG[0]));addr_cnt U0_instance(CPi,K,ROMaddr,Address);SineROM ROM_inst(.address(ROMaddr),.clock(CPi),.q(Qsine));squwave U1(CPi,RSTn,Address,Qsquare);always @(posedge CPi)begincase(WaveSel)2'b01:WaveValue=Qsine;2'b10:WaveValue=Qsquare;default:WaveValue=Qsine;endcaseend

endmodule

三、实验实现

使用DE2-115开发板来验证上述设计,根据DE2-115引脚配置表配置引脚。

SW16\SW17用来选择输出波形的种类,LEDG0作为PLL的锁定指示。

module DE2_115_DDS_top(CLOCK_50,KEY,SW,GPIO_0,LEDG);input CLOCK_50;input [3:3] KEY;input [17:0] SW;output [12:0] GPIO_0;output [0:0] LEDG;wire CLOCK_100;assign GPIO_0[12]=CLOCK_100;wire RSTn=KEY[3];wire [1:0] WaveSel=SW[17:16];wire [12:0] K=SW[12:0];wire [11:0] WaveValue;assign GPIO_0[11:0]=WaveValue;DDS_top DE2(CLOCK_50,RSTn,WaveSel,K,WaveValue,LEDG,CLOCK_100);

endmodule

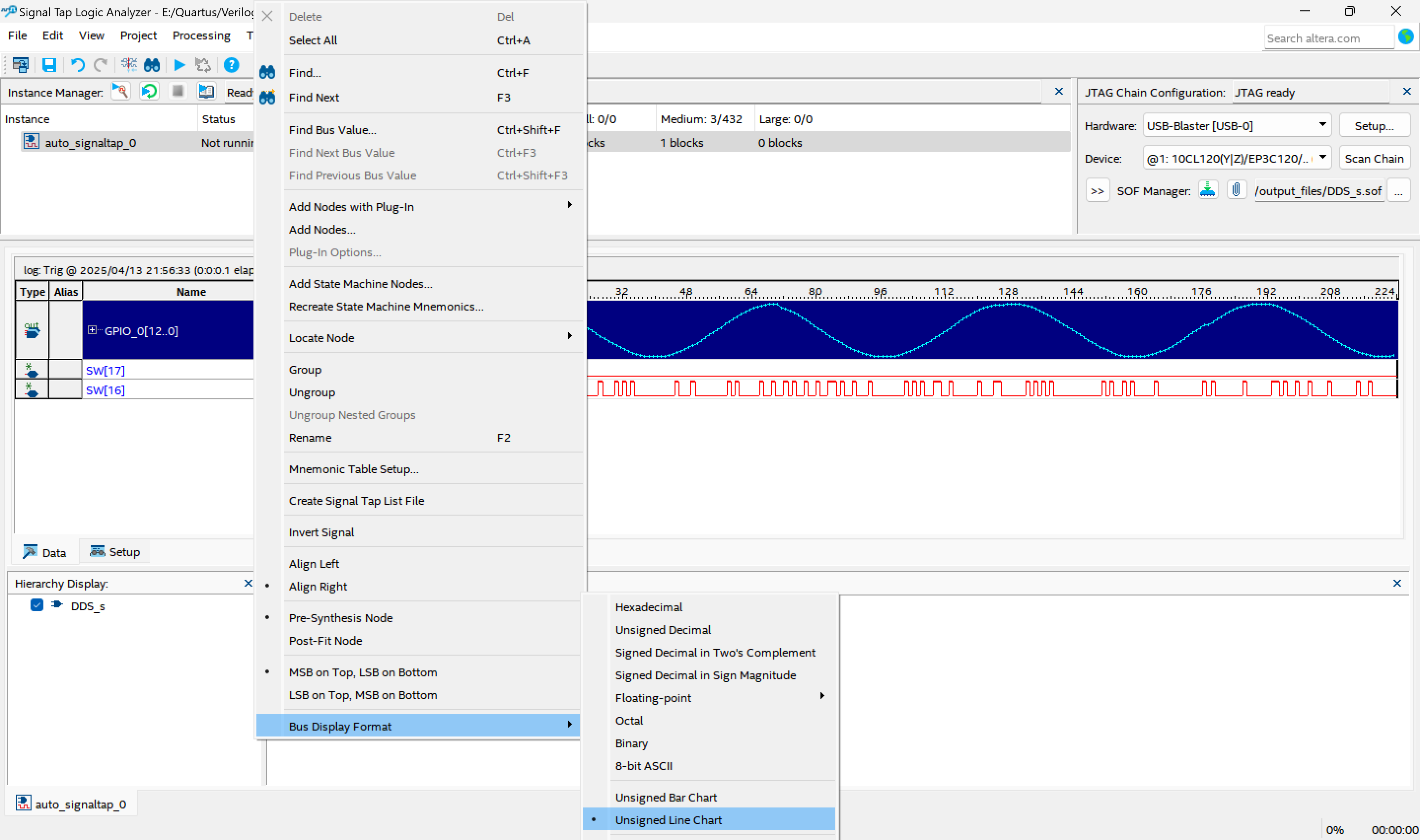

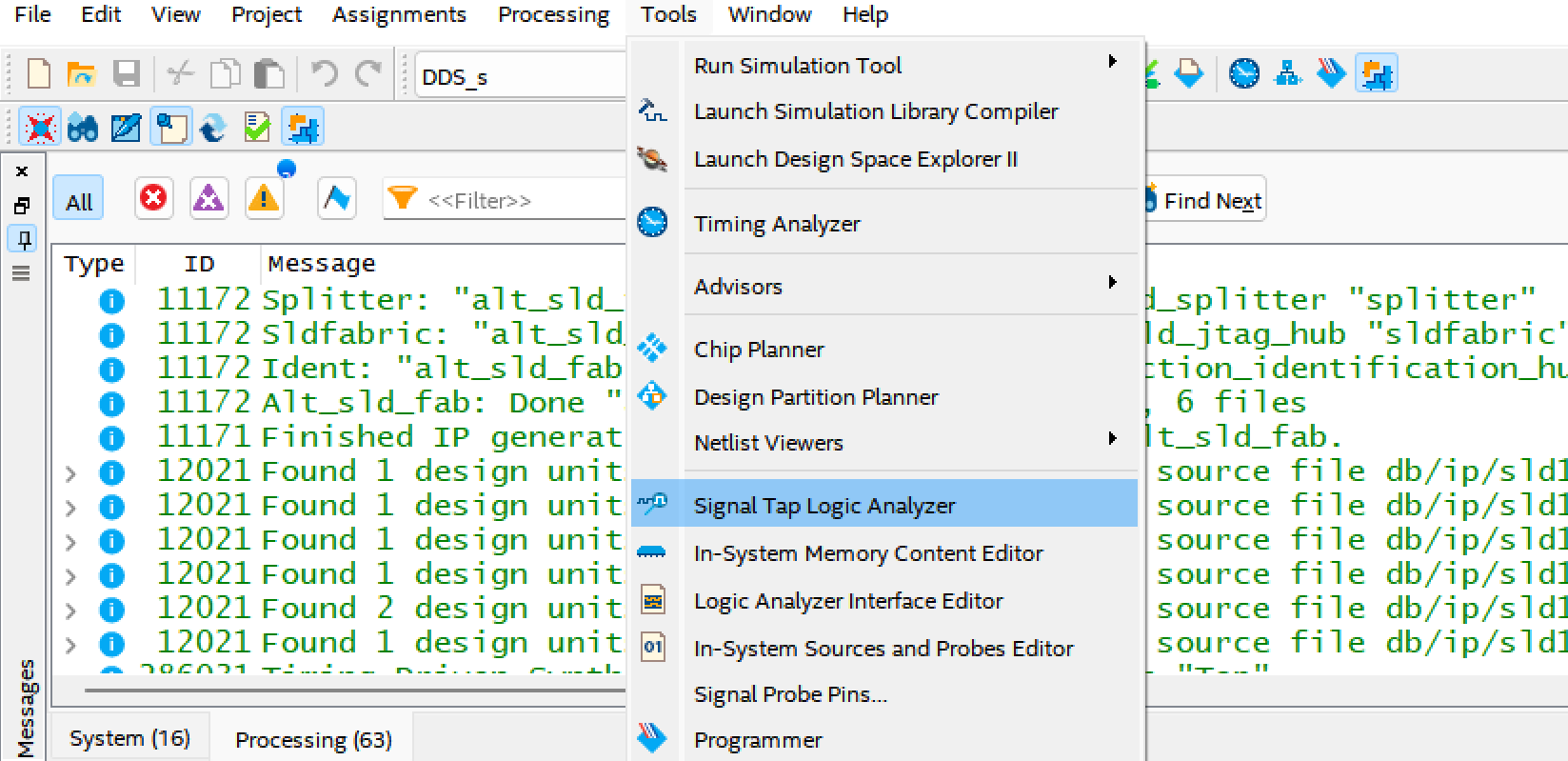

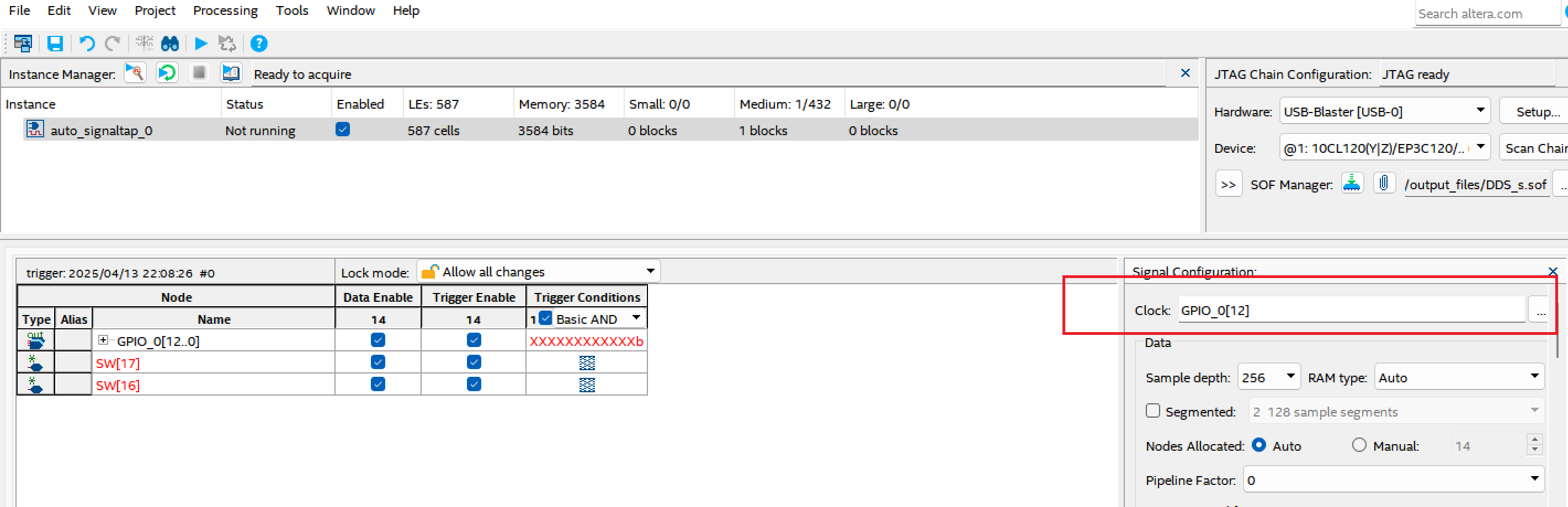

编译通过后,再次点击一次Start Analysis & Systhesis,然后就可以使用SignalTap ll实时测试输出波形的离散数据,选择Tools->SignalTap ll Logic Analyzer。

注意,时钟Clock配置要选择GPIO_0[12]

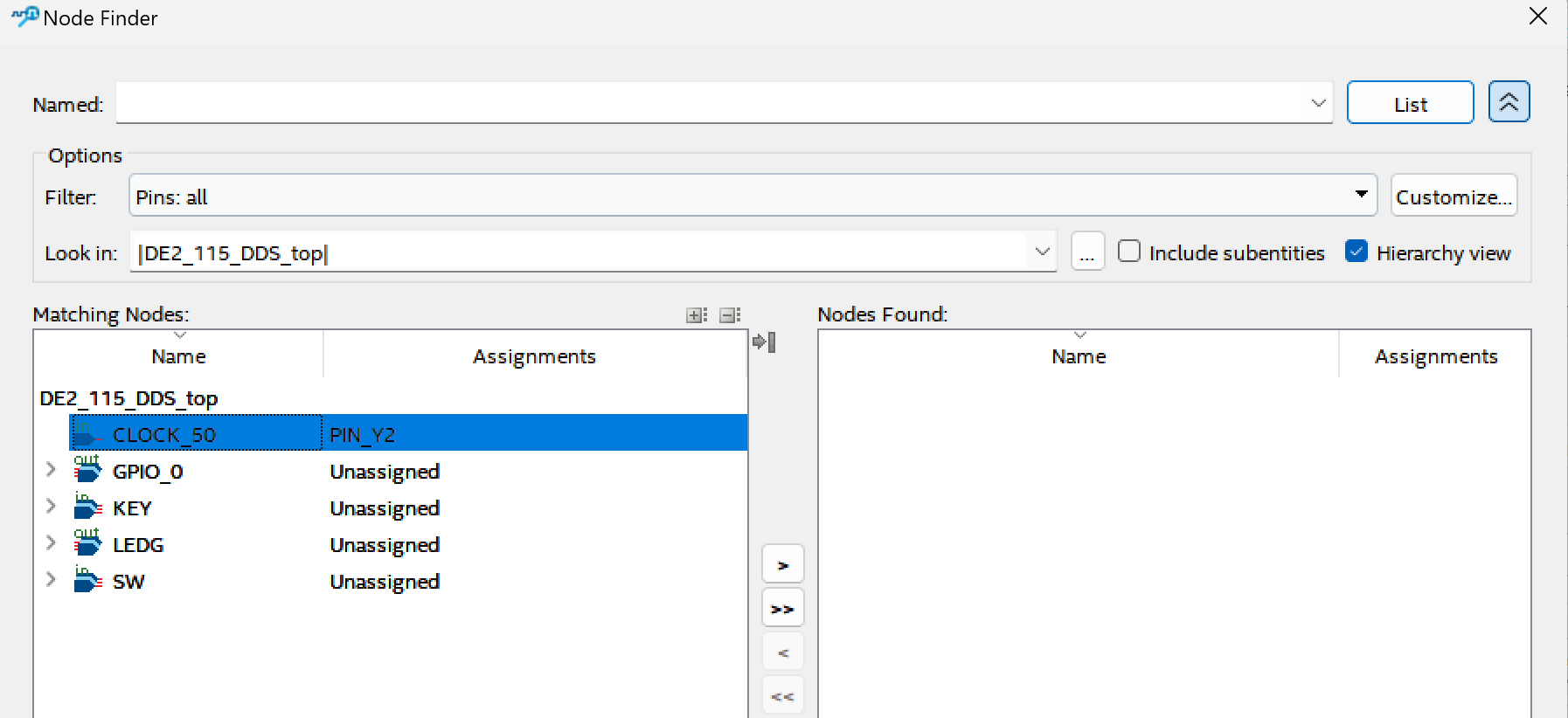

Node添加只需要双击Setup上面的空白处即可添加。

更改Flitter,然后点击List

确认无误后,保存SignalTap文件,点击编译,连接DE2-115。

操作完成后,拨动SW16和SW17,波形会发生变化。GPIO_0的波形可能会很奇怪,需要你右键选择格式,这样才会有波形图。