uCOS3实时操作系统(系统架构和中断管理)

文章目录

- 系统架构

- 中断管理

- ARM中断寄存器相关知识

- ucos中断机制

系统架构

- ucos主要包含三个部分的源码:

1、OS核心源码及其配置文件(ucos源码)

2、LIB库文件源码及其配置文件(库文件,比如字符处理、内存管理)

3、CPU板级源码及其配置文件(用于适配不同的开发板) PendSV中断的实现,裸机是不需要实现这个函数的,ucos的任务切换就是通过软件触发PendSV中断调用汇编函数OSStartHighRdy实现。SysTick中断的实现,裸机中通过此中断实现系统时钟HAL_TICK,ucos也是通过该中断调用OS_CPU_SysTickHandler();实现。- 以上两个中断接口需要在中断向量表进行修改,注意SysTick的中断函数是自己手动实现不需要修改名称,添加

OS_CPU_SysTickHandler();即可,而PendSV是ucos汇编源码实现,需要在中断向量表修改接口。

中断管理

ARM中断寄存器相关知识

- 外部中断的优先级设置通过NVIC寄存器设置,ARM Cortex-M 的

NVIC最大可支持 256 个中断源,其中包括 16 个系统中断和 240 个外部中断。然而芯片厂商一般情况下都用不完这些资源,以正点原子的战舰开发板为例,所使用的STM32F103ZET6 芯片就只用到了10 个系统中断和 60 个外部中断。

ARM Cortex-M 使用了 8bit 位宽的寄存器来配置中断的优先级,这个寄存器就是中断优先级配置寄存器,因此中断优先级的配置范围就应该是 0 ~ 255。但是芯片厂商一般用不完这些资源,对于 STM32,只用到了中断优先级配置寄存器的高四位[7:4],低四位[3:0]取零处理,因此 STM32 提供了最大 2^4^=16 级(0~15) 的中断优先级等级。

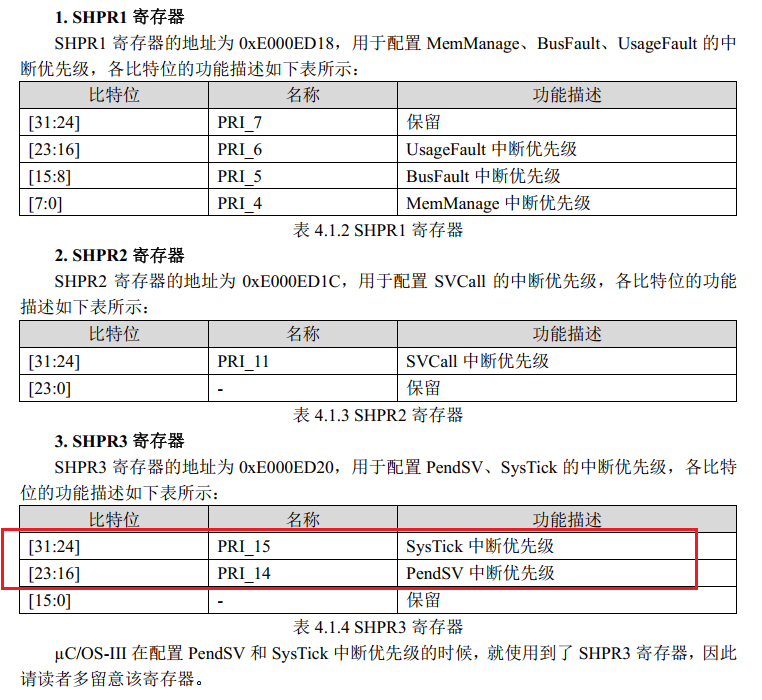

进一步的,ARM Cortex-M 还使用了抢占优先级和子优先级的机制,在 STM32 上使用 µC/OS-III 时,使用中断优先级分组 4(NVIC_PriorityGroup_4)即优先级配置寄存器的高四位全部用于抢占优先级,不使用子优先级,那么这么一来只需要设置中断的抢占优先级即可。 - 系统中断的优先级通过以下三个寄存器设置:

- 系统中断屏蔽主要通过三个寄存器实现:

PRIMASK:PRIMASK 寄存器有 32bit,但只有 bit0 有效,是可读可写的,将 PRIMASK 寄存器设置为 1 用于屏蔽除 NMI 和 HardFault 外的所有异常和中断,将 PRIMASK 寄存器清 0 用于使能中断。

FAULTMASK:FAULTMASK 寄存器有 32bit,但只有 bit0 有效,也是可读可写的,将 FAULTMASK寄存器设置为 1 用于屏蔽除 NMI 外的所有异常和中断,将 FAULTMASK 寄存器清零用于使能中断。

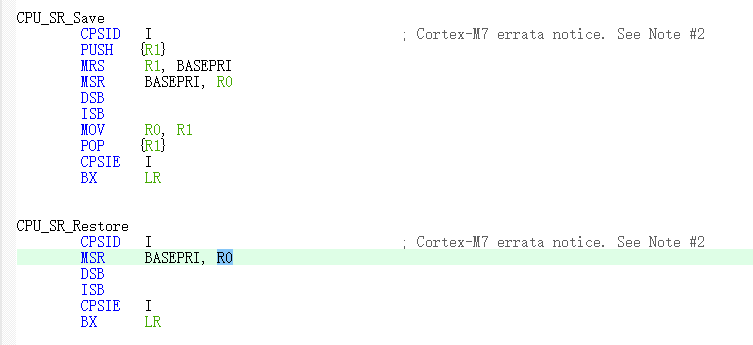

BASEPRI:BASEPRI 有 32bit,但只有低 8 位[7:0]有效,也是可读可写的。 BASEPRI 寄存器比起 PRIMASK 和 FAULTMASK 寄存器直接屏蔽掉大部分中断的方式, BASEPRI 寄存器的功能显得更加细腻,BASEPRI 用于设置一个中断屏蔽的阈值,设置好 BASEPRI 后,中断优先级低于 BASEPRI 的中断就都会被屏蔽掉, µC/OS-III 就是使用 BASEPRI 寄存器来管理受 µC/OS-III管理的中断的,而不受 µC/OS-III 管理的中断,则不受 µC/OS-III 的影响。

ucos中断机制

-

中断优先级可以理解为抢占优先级,任务优先级可以理解为子优先级

-

在ucos中,

PendSV的中断优先级设置为最低级16,因此只要其他任务中断优先级大于16,ucos就先执行中断里面的内容,然后才进行任务切换函数(只是个函数不是任务) -

在ucos中将

BASEPRI设置为4,即受ucos控制的最高优先级为4 -

OS_CPU_SysTickInit()对 SysTick 进行配置, 设置systick的中断优先级为4,systick中断优先级大于一切,毕竟是系统心跳,但是此处会出现一个问题(如果我们使用临界区包含关闭所有受ucos控制的中断的时候,系统时钟也不会发生中断) -

控制所有中断,将前面所提到的

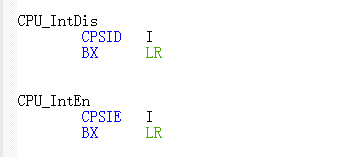

PRIMASK或者FAULTMASK置为 1 实现CPU_IntDis ; 关闭所有中断 CPU_IntEn ; 打开所有中断

-

控制受ucos管理的中断,通过将BASEPRI的值设置为 4 或者 0 即可进行关闭和打开,0 即为打开所有中断,4 即为优先级大于4的关闭。

#define CPU_SR_ALLOC() CPU_SR cpu_sr = (CPU_SR)0、 CPU_SR_ALLOC(); /* 必须定义在所有局部变量之后 */ CPU_SR_Save ; 保存中断状态,并关闭受 µC/OS-III 管理的中断 CPU_SR_Restore ; 恢复中断状态

-

临界区包含(其实就是调用控制受ucos管理的中断的函数)

CPU_SR_ALLOC(); /* 必须定义在所有局部变量之后 */ /* 非临界区代码 */ CPU_CRITICAL_ENTER(); /* 进入临界区 */ /* 临界区代码 */ CPU_CRITICAL_EXIT(); /* 退出临界区 */ /* 非临界区代码 */ -

锁定任务调度器,仅仅PendSV中断不产生

OS_ERR err; OSSchedLock(&err); 锁定 uC/OS-III 的任务调度器 OSSchedUnlock(&err); 恢复 uC/OS-III 的任务调度器 -

SysTick 的中断服务函数为例,展示函数

OSIntEnter()和函数OSIntExit()的使用,函数OSIntEnter()只是简单地更新了全局变量 OSIntNestingCtr 的值, 而函数OSIntExit()除了更新全局变量OSIntNestingCtr 的值,同时还会根据需要进行任务切换。:void OS_CPU_SysTickHandler(void) { CPU_SR_ALLOC(); CPU_CRITICAL_ENTER(); /* 进入中断后,先调用函数 OSIntEnter() */ OSIntEnter(); CPU_CRITICAL_EXIT(); /* 中断服务函数的内容 */ OSTimeTick(); /* 中断返回前,调用函数 OSIntExit() */ OSIntExit(); }