【PCIE配置空间】

1 PCIE配置空间

1.1 软件如何知道PCIE设备是Swith,RC还是EP?

–软件通过读取寄存器信息。

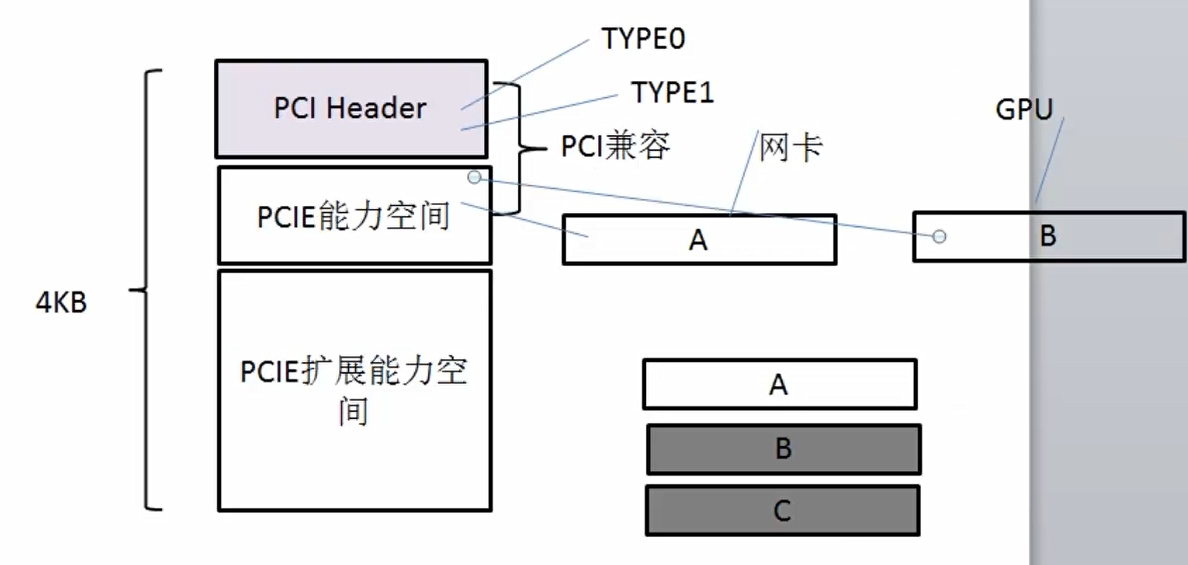

PCIE配置空间• PCIE寄存器;--PCIE配置协议规定必须实现的空间。--PCIE存在两种配置空间Type0/Type1;--Type0配置空间EP设备必须实现;--Type1配置空间RC/Switch设备必须实现;• PCIE配置空间具体大小 --1DW = 4Byte

图–:

• PCIE每个设备都有4KB的配置空间• 4KB配置空间前64DW(即256Byte)与PCI兼容保持一致;• 960DW为PCIE扩展寄存器空间;

PCIE兼容配置空间:

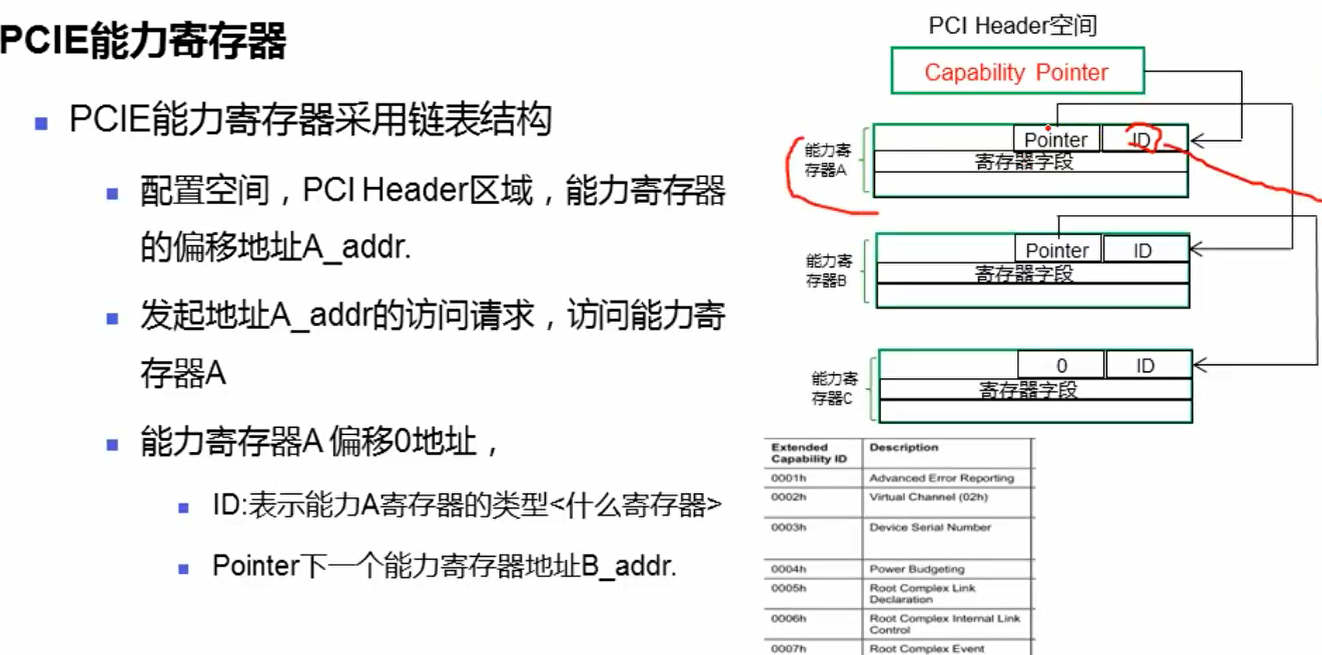

1.PCIE兼容配置空间包含PCI Header--64Byte空间和Capability--192Byte空间;2.Header空间分为Type0和Type1两种:Type0配置空间EP设备必须实现;Type1配置空间RC/Switch设备必须实现;3.Capalitiy空间--以链表形式组织的扩展功能寄存器:能力寄存器空间,实现可选择实现的寄存器;但如下寄存器必须实现:PCIE Capality; Power Management; MSI/MSIX;4.能力寄存器采用链表结构;```c//==这是从0到大进行排列;Offset 0x40: | Cap ID (8b) | Next Ptr (8b) | Cap Data (16b) | → 4字节对齐Offset 0x80: | Cap ID (8b) | Next Ptr (8b) | Cap Data (16b) | → 下一个对齐项```ID:表示能力A寄存器的类型<什么寄存器>;Pointer表示下一个能力寄存器地址B_addr;其图如下所示:

例如:PCIE能力寄存器中的PM/MSI寄存器,软件如何进行获取呢?

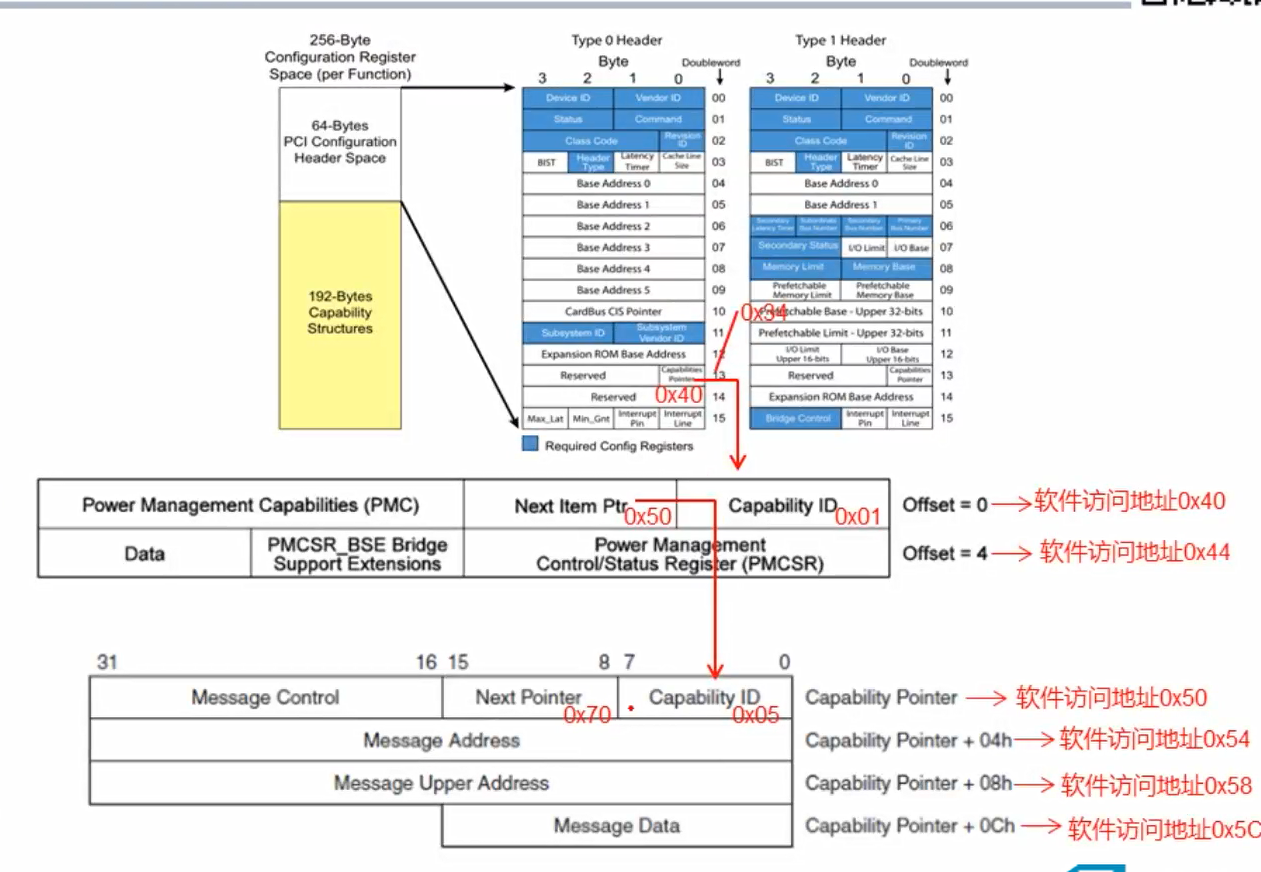

Steps:1.系统软件发起addr:0x34的读请求,访问PCI header Capalibity point寄存器(起始是固定的);2.系统软件读取addr:0x34 pointer:0x40,返回结果表示PCIE下一组寄存器的地址为0x40;3.系统软件发起addr:0x40的读请求;4.系统软件读取:addr:0x40, data:{0x50,0x1};ID:0x1表示类型为PM寄存器;Next Pointer: 0x50表示访问下一个能力寄存器的地址位0x50;5.系统软件再进一步读取0x50地址,读取数据{0x70,0x05};ID:0x5表示位MS寄存器;NextPointer: 0x70表示访问下一个能力寄存器的地址为0x70;6.通过查手册可知:取addr:0x54,0x55,0x56分别配置MSI中断地址和数据;0x54:表示Message lower address; 0x58: Message upper address;0xC0:表示Message data;

步骤图如下:

小结:链表是单链表结构,就是软件的数据结构,只能进行便来访问,不能通过index索引来访问;