6.数据手册解读—运算放大器(三)

7、应用和实现

7.1应用信息

TLV916x 系列提供了出色的直流精度和交流性能。 这些器件的工作电压高达 16V, 并提供真正的轨到轨输入/输出、 低失调电压、失调电压漂移以及 11MHz 带宽和高输出驱动。TLV916x适用于16V工业应用。

7.2 典型应用

7.2.1 低边电流测量

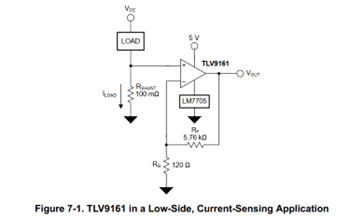

下图是一个低边电流测量电路,可以用于电机的电流检测、电磁阀闭环控制等。

7.2.1.1 设计需求

该电路的设计目标如下:

• 负载电流(需要检测的电流):0A to 1A

• 运放输出电压: 4.9V

• 采样电阻的最大电压(被放大的最大电压): 100mV

7.2.1.2 设计计算过程

Figure 7-1电路的传递函数为:

![]()

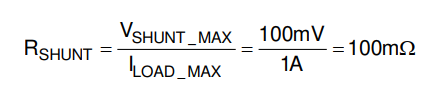

采样电阻的选型:

负载电流(ILOAD)流过采样电阻(RSHUNT)会产生一个压降,这个压降最大为100mV。并且负载电流(ILOAD)为1A,故采样电阻的阻值为:

注:TI只给出了采样电阻的阻值,这里还需要考虑一个点——功率。改采样电阻的需要的最小功率为

这里只是简单说一下,其实还有封装、精度、温漂、降额等需要考虑。在设计BLCD驱动电路的时候会讲。

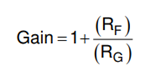

放大增益计算:

放大器的输出范围为0到4.9V,按照输入输出的关系,增益计算如下:

通过设计RF 和RG就可以选择合适的增益。增益和RF、RG的关系如下:

将RF/RG的比值设为48即可。TI设计的阻值为:RF和RG被选定为5.76kΩ和120Ω。(这里留一个问题,电阻的阻值比可以确定,具体阻值是怎么计算的)。

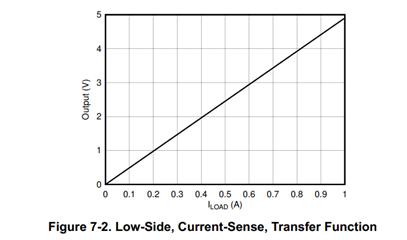

7.2.1.3 应用曲线

采样电流和运放输出电压的关系如下图所示:

7.2.2 缓冲器复用

TLV916xS 关断器件可通过配置,用于创建缓冲多路复用器。 可将输出连接在一起,而关断引脚可用于选择所需通道。 放大器电路的禁用转换比启用转换发生得快,因此放大器呈现出“ 先断后合”的开关拓扑。

当处于关断状态时,放大器输出进入高阻抗状态,因此将多个通道输出连接在一起时,没有总线争用的风险。此外,输出与输入是隔离的, 因此无须担心每个通道输入处的阻抗与输出处的阻抗相互耦合。

此外, 这种拓扑结构使用放大器而不是 MOSFET 开关, 因此消除了多路复用器的其他常见问题, 例如电荷注入或 RON 效应引起的信号误差。

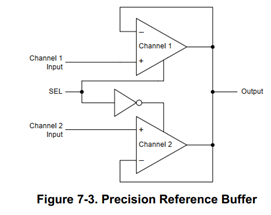

Figure 7-3展示了基本 2:1 多路复用器的拓扑示例。当 SEL 较低时, 通道 1 被选中并运行; 当 SEL 较高时, 通道 2被选中并运行。

7.3 供电电源

TLV916x 的额定工作电压范围是2.7V 至 16V。电源电压大于 20V 会对器件造成永久损坏。将 0.1µF 旁路电容器置于电源引脚附近, 以减少来自高噪声电源或高阻抗电源的耦合误差。

7.4 LAYOUT

7.4.1 LAYOUT指南

为了实现器件的最佳工作性能,应采用优化的PCB布局设计,具体建议如下:

电源噪声抑制

- 电源噪声可能通过供电网络和运放本体耦合至模拟电路。建议在每个电源引脚与地之间就近布置低ESR(等效串联电阻)的0.1μF陶瓷去耦电容,以构建低阻抗的局部供电网络。

- 对于单电源应用,在V+与地之间配置单个去耦电容即可满足需求。

接地系统设计

- 采用独立的模拟地和数字地是抑制噪声最有效的措施之一。推荐使用多层PCB的专用接地层,既可改善散热又能降低EMI干扰。

- 需确保模拟地和数字地在物理上隔离,同时注意控制接地电流路径。

布线优化

- 为降低寄生耦合,敏感信号线(如输入走线)应与电源线/输出线保持足够间距。若必须交叉布线,应使敏感信号线与噪声线呈正交走向而非平行布置。

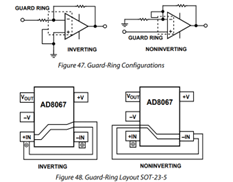

- 在关键走线周围设定驱动型低阻抗保护环。保护环可以显著减少附近走线在不同电势下产生的泄漏电流。

保护环在手册里描述的不多。可以参考一下ADI的设计:

外围元件布局

- 关键外部元件(如反馈电阻RF和RG)应尽可能靠近器件引脚布置。将反馈网络贴近运放反相输入端可有效减小寄生电容影响。

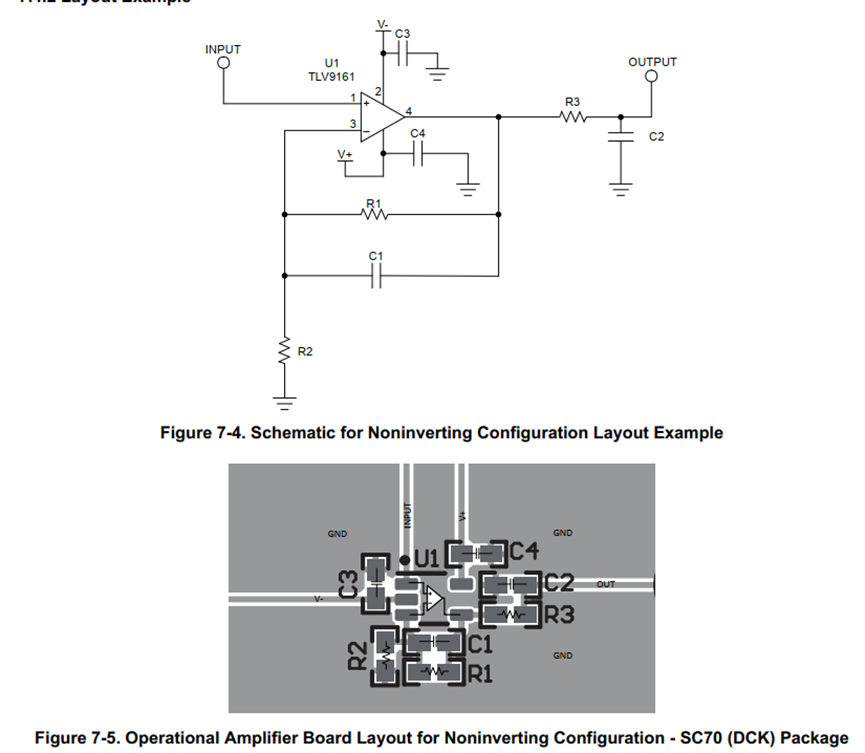

7.4.2 Layout 示例

B站唐老师讲到,运放的反向输入端与GND之间不要接电容。引脚附近不要铺铜,所有层都不要,一挖到底。