TDR阻抗会爬坡? 别担心,不是你的错,你只是不够了解TDR!

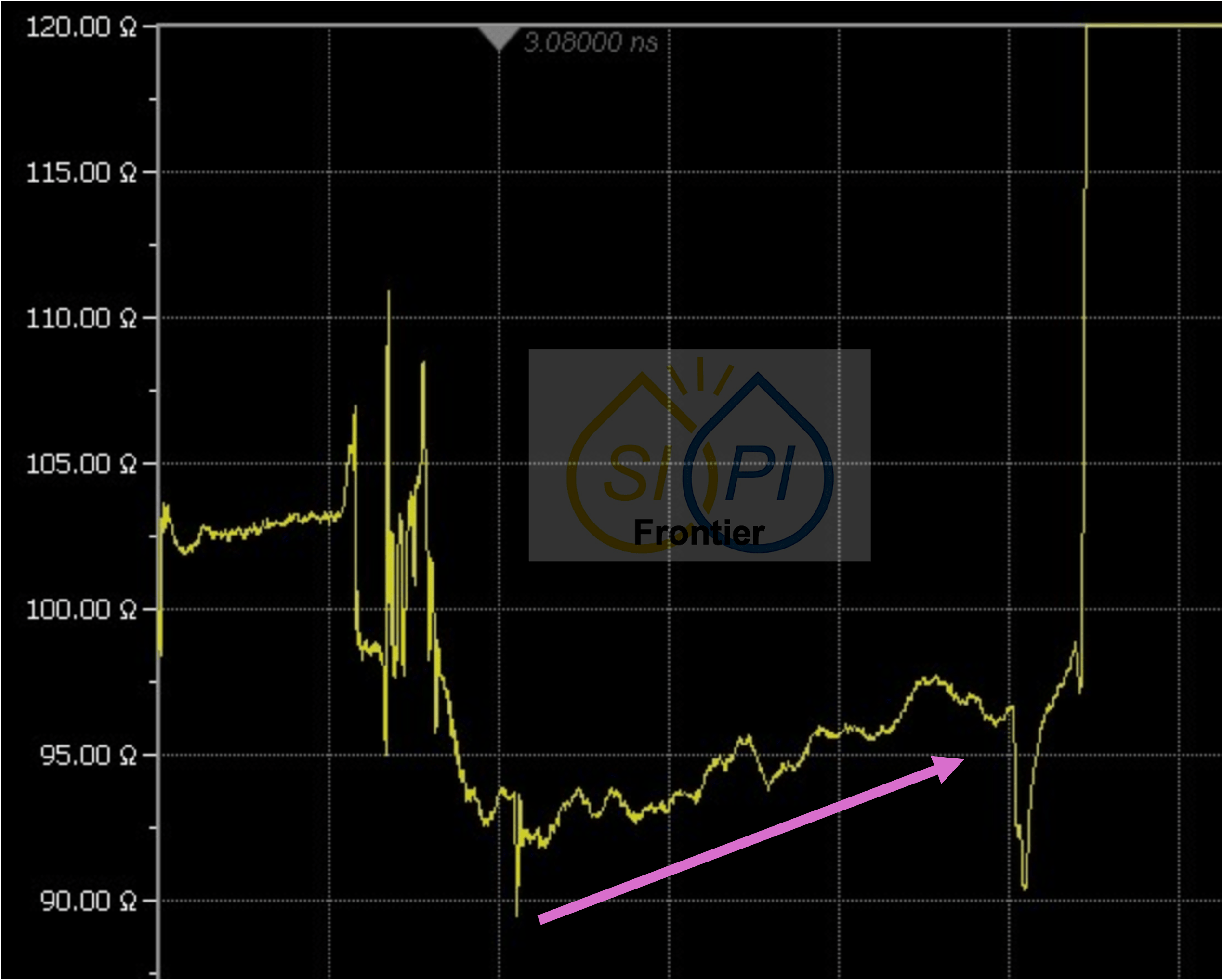

在背板系统或任何长走线设计里,你大概都碰过这画面:

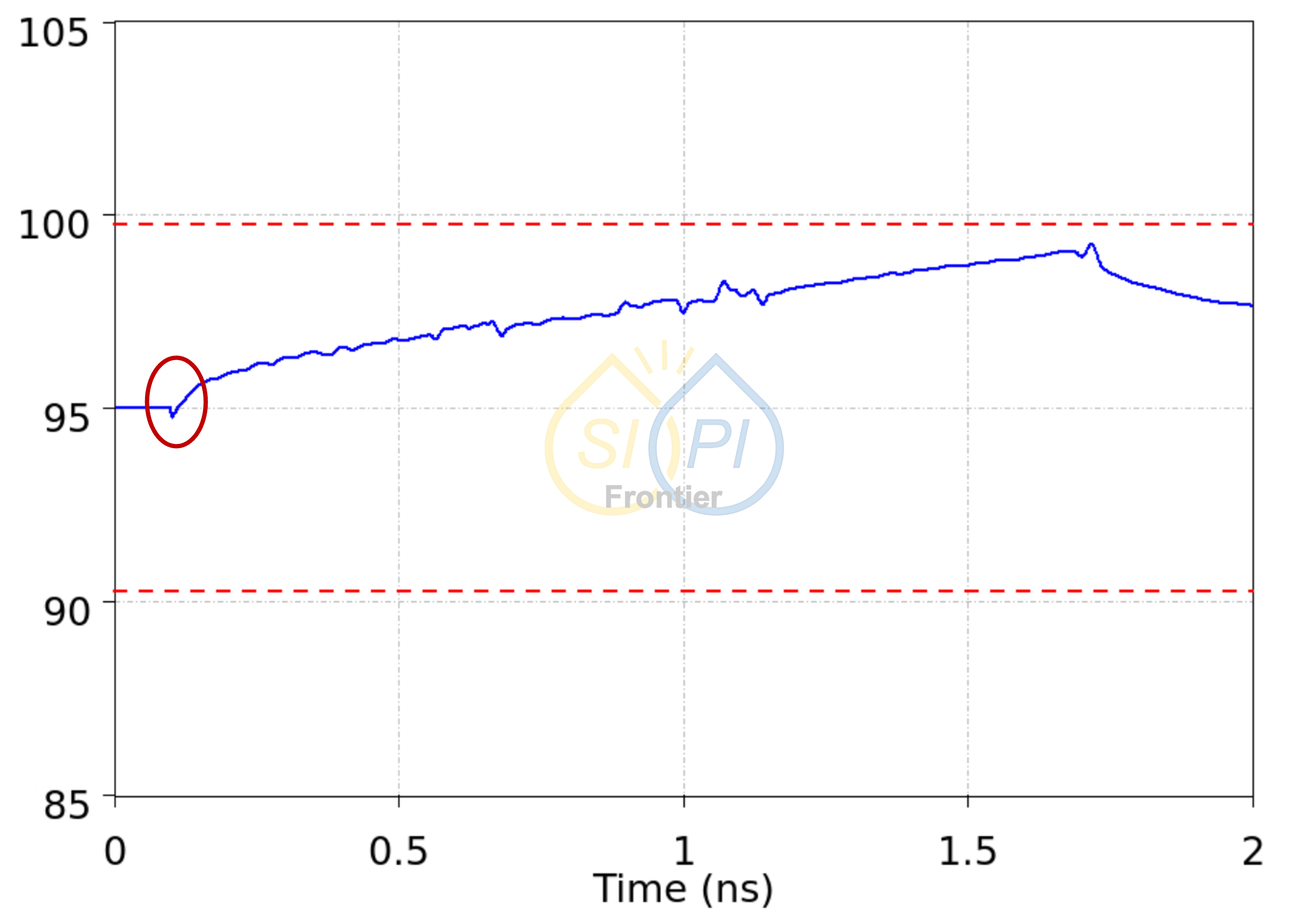

TDR 曲线一开始乖乖在 92 Ω,但越往末端、阻抗越爬越高,来到最高 97 Ω,心里瞬间凉半截

😒 ,「难不成... 板厂又翻车了吗?」

然后,当你去找板厂理论时,人家跟你讲,这很正常啊,咱们测了好几百张板子了,数据都是这样子跑的,还拿出过往的测试图给你看。 这到底...?

🔑 做任何决定前,先不要怀疑别人,想想自己是不是哪里搞错了。 🔑

这其实是TDR模拟或是测试时很常见的现象,尤其是当走线设计越长,这个爬坡的现象越明显,绝对不是说你的设计有问题,至于为什么会发生? 本文带您从为何TDR被如此广泛地应用在SI领域,以及背后的基础理论,再来解析为何传输线测试时会有往上爬的现象,让您对TDR有更深一层的认识!

为何使用TDR?

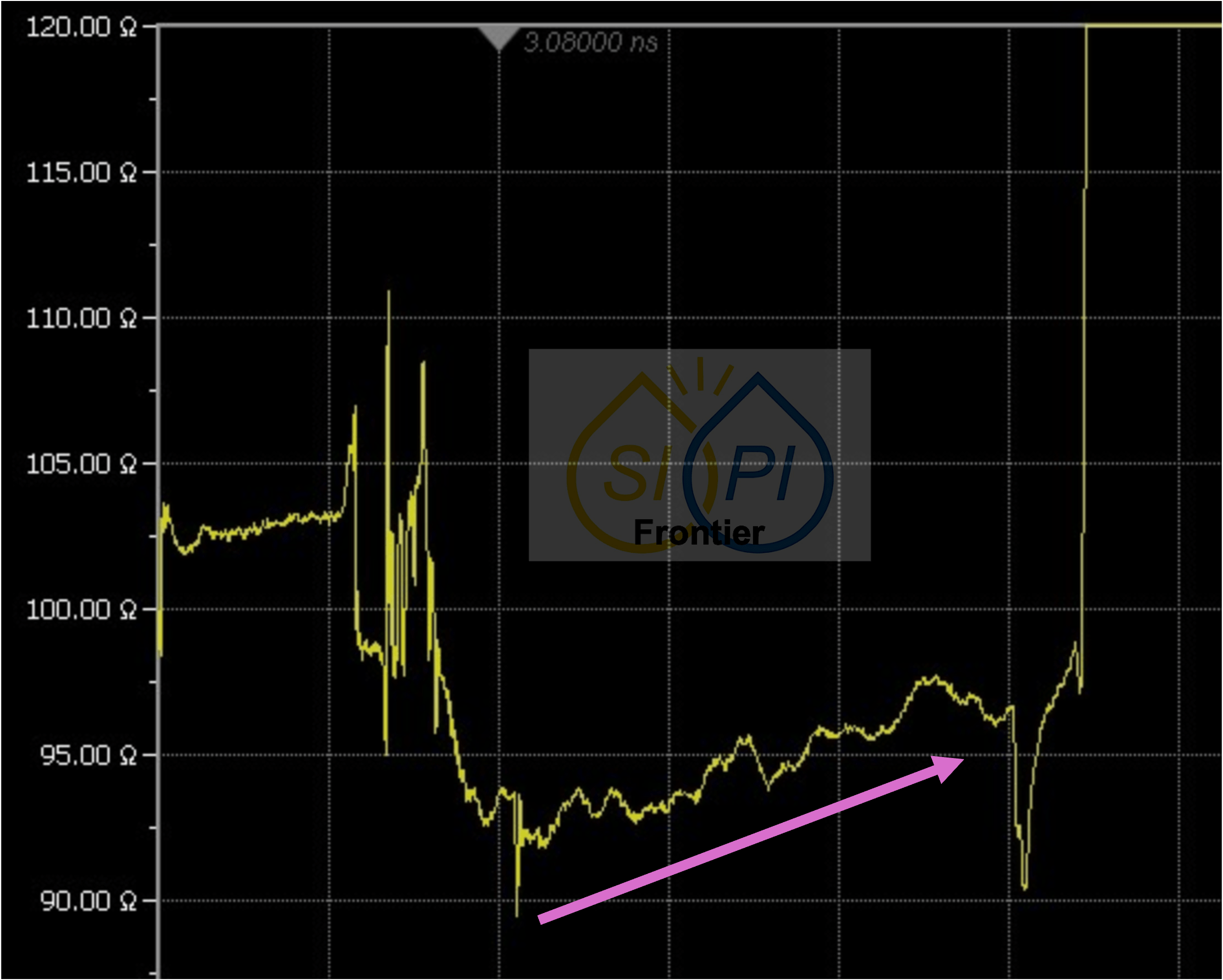

TDR(Time-Domain Reflection),其实就像拿手电筒往线路里照,哪里断、哪里接不好,一眼就能看出来。 很多行业都得靠它找线路的哪里发生开路,而在信号完整性这圈子,TDR更是我们的日常武器。 设计阶段,工程师先在电脑里把每个零件,像是 Via、Connector、Trace,统统放到模拟软件里面去跑模拟,算出它们应该有的阻抗,确保通道的阻抗匹配。 板子打样做好后,还得把实际的板子,透过网络分析仪或阻抗量测机台,扫一遍真实阻抗曲线。 最后再把模拟图叠上量测图,比对每个波峰、波谷的位置是否接近,阻抗值差了多少,并确认设计时设定的参数,如材料的DK/DF是否与实际的一致,必要时还得透过切片,看看板子加工后的厚度与线宽/线距,整体比对起来如果很吻合,那我们才可以说模拟是靠谱的。

说到TDR为什么这么好用,最大的原因就是因为它可以单靠一条步阶波、只用一个 Port,就能把整条通道的阻抗分布扫得清清楚楚。 想想看,要量损耗还得准备两边 Test fixture、校正、锁治具,流程相对冗长; 而TDR只要简单一个Port,屏幕立刻画出曲线,这种「单点注射、全段成像」的特性,真的省下我们许多的时间。

但很多人就会问:TDR 看不到损耗,那频域规格怎么办? 其实,只要阻抗匹配做得够好,损耗通常就不会差到哪去,真的要确认规格,再透过双埠测试验证一下即可,工作吗... 还是得尽量省心呀。

TDR基本理论介绍

TDR除了可以单靠一个Port就得到通道的阻抗外,其实也可以拿来计算传输线的Delay,或是两两对象之间的距离,甚至是拿来求得等效介电常数!

阻抗分析

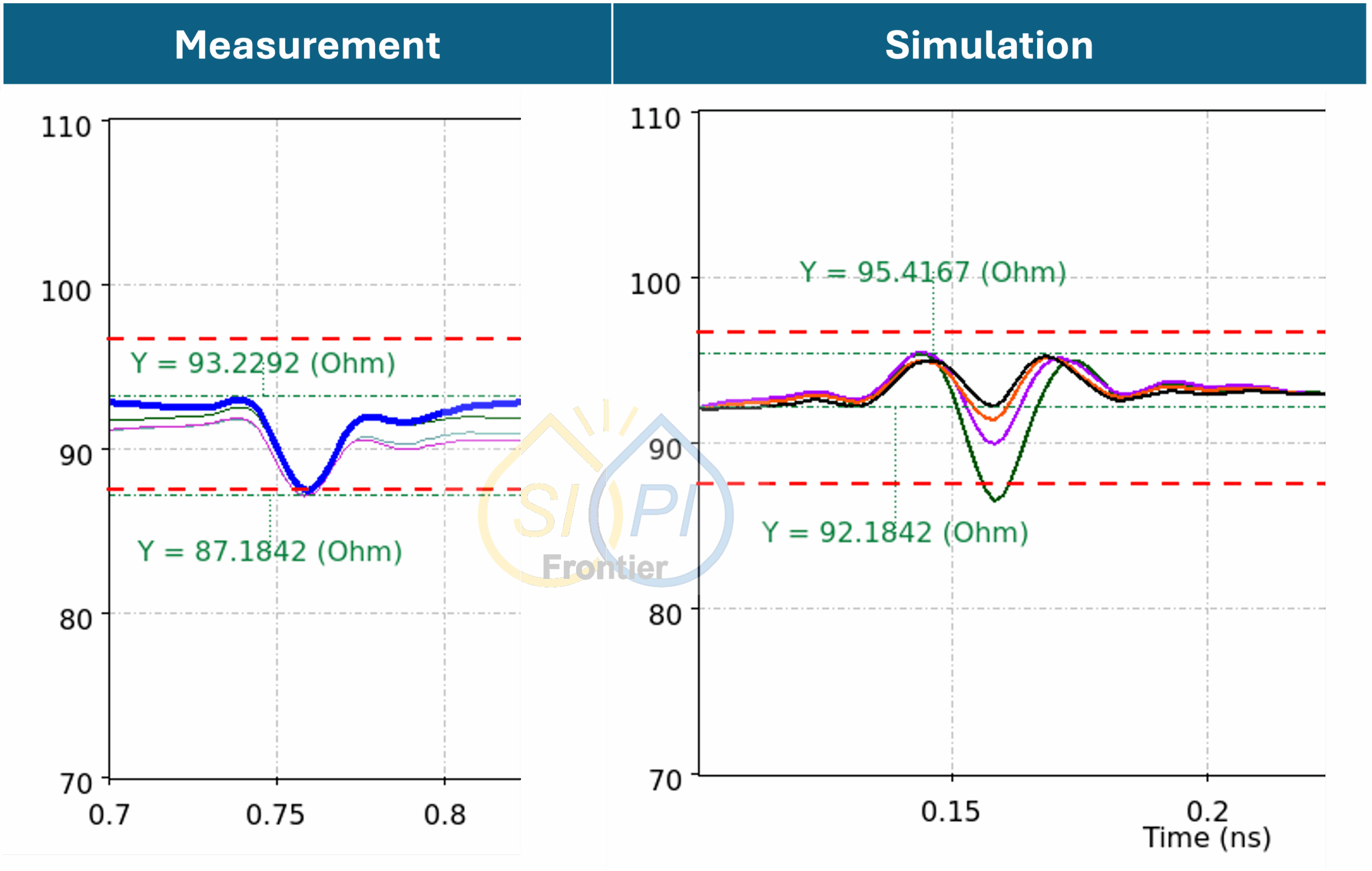

为什么TDR这么厉害,可以单单使用到一个Port就可以得到整条路径的阻抗?

其实原理很简单,透过分压定理,稍微换算一下就可以得到答案!

下面这张图... 应该不需要多做解释了吧 😁

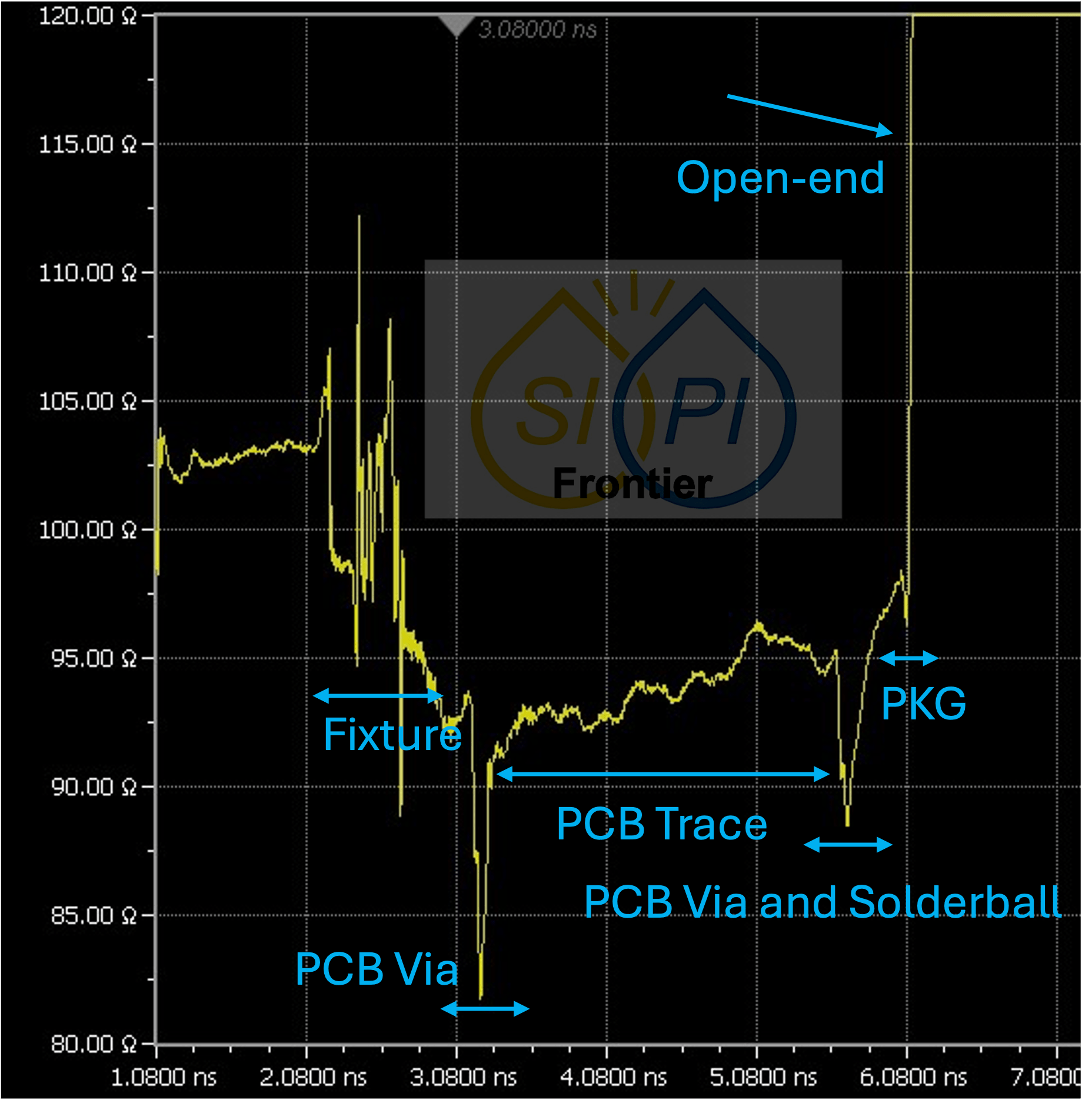

从测试仪器如网络分析仪,你看到的TDR图大概率会长这个样子。

开头会是一段测试治具Test Fixture,通常这段我们会把它De-embedded,或是做Time-domain gating把它拿掉,这样数据看起来会稍微清楚些,不移除也是还好,不太会大幅度地影响测试结果,但是要小心一点,如果Test Fixture的设计很差很差,阻抗不匹配的太跨张,很容易导致待测物的数据严重失真!

接着是待测物通道的数据,例如PCB的SMT pad、过孔Via、传输线Trace、封装PKG的Solderball皆会囊括其中。 可以看到这些零件分别有各自的阻抗表现,像开头第一个掉落点,就是SMT pad与其上的Via组成的电容性负载所造成的低阻抗,因为TDR有分辨率的关系,造成SMT pad与Via在这边难以分辨(所以我们在这篇文章有提到强烈建议做SMT pad+Via的共模拟去做两者间的设计)。

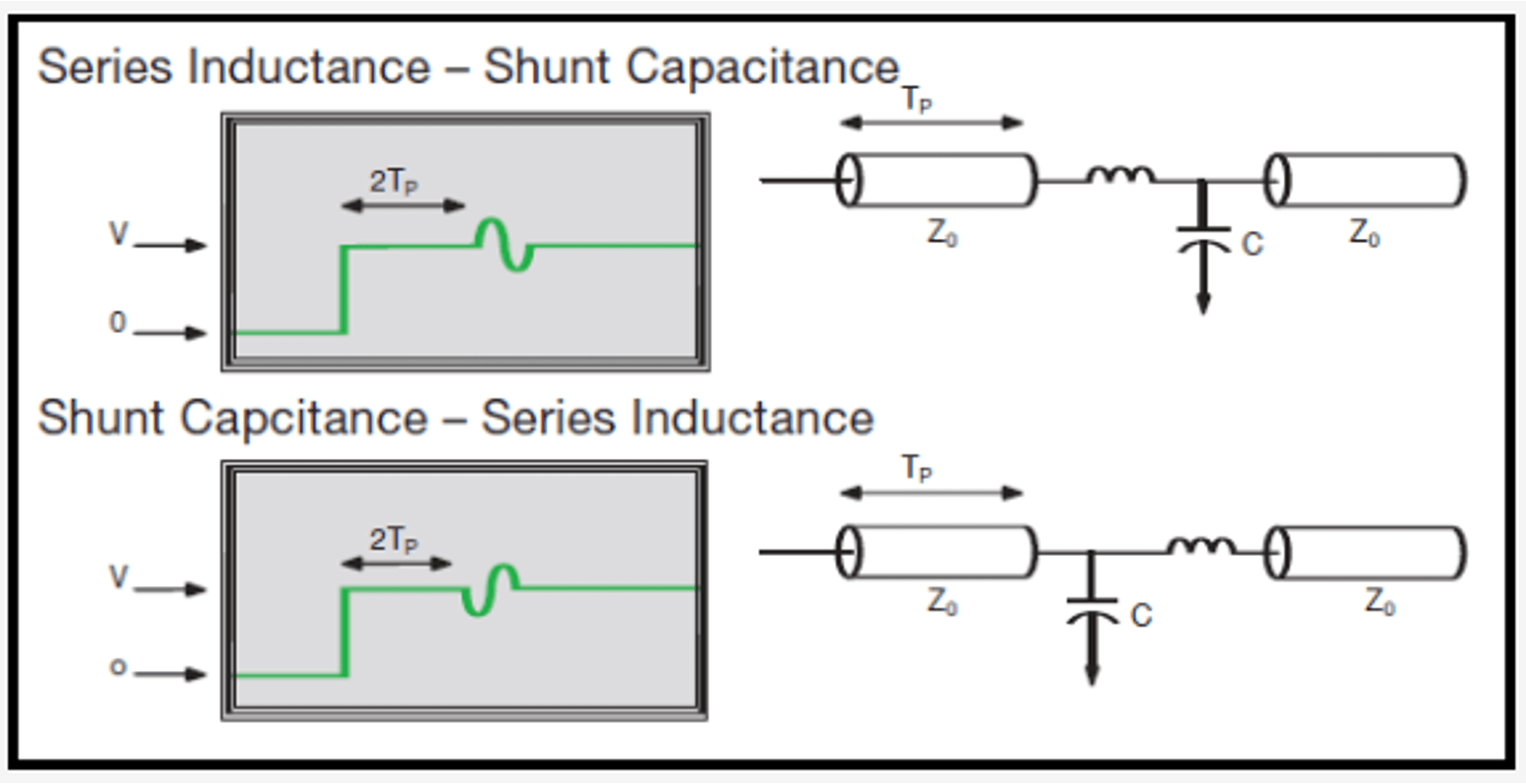

电感性与电容性负载

我们在看TDR阻抗图时,会很明显看到阻抗曲线呈现上上下下的走势,通常我们可以依据这条曲线的起伏来判断这个时间点是电感性负载还是电容性负载来主导。

由于电感在高频属于“正”阻抗,因此如果阻抗曲线往上跳,代表这个时间点是电感性负载。

而电容在高频属于“负”阻抗,所以如果阻抗曲线往下跳,则表示电容性负载在此时主导了阻抗结果。

(这篇文章对于TDR分析写得很好,也建议各位去看)

电感在高频属于“正”阻抗:

ZL=jωL

电容在高频属于“负”阻抗:

ZC=−j1ωC

所以意思就是,如果你觉得阻抗过高,那就得想办法在那个位置增加电容; 如果阻抗过低,那就搞个电感给它,把阻抗补偿回来即可!

如果大家对补偿机制有兴趣,我们再额外讨论啰~ 🤭

Delay分析

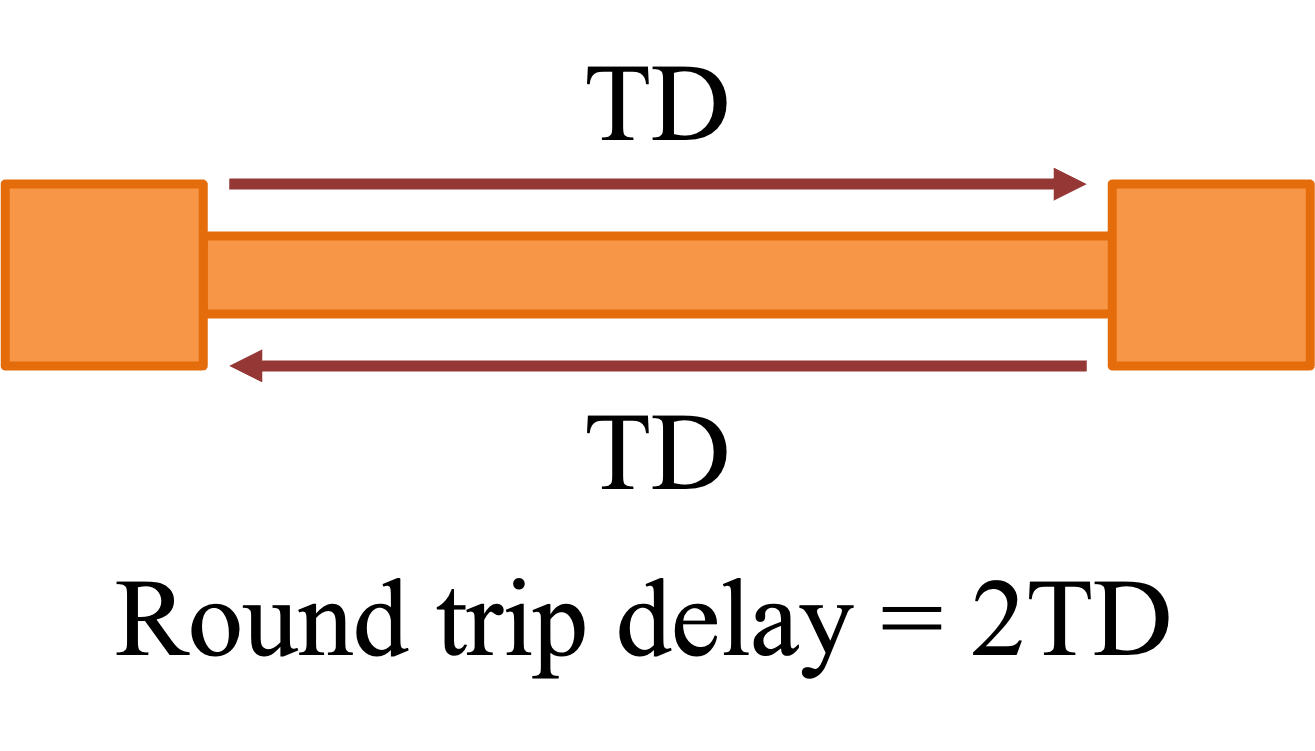

TDR 是纯时域的量测方法:我们把一个上升时间很快的步阶波打进待测物,波一路向前跑,当它遇到不连续点时,因为阻抗不匹配,而产生反射波。 反射波沿原路折返回仪器,每个阻抗不连续的「出现时间」,就代表这个阻抗不连续点离源头多远。 换句话说,TDR也可以拿来判断待测物的长度,或是两两对象之间的距离。

不过要记得一件事:因为步阶波从源头跑到不连续点再反射回来,实际走了「去程+回程」两倍的路,所以仪器上显示的时间自然也是两倍。

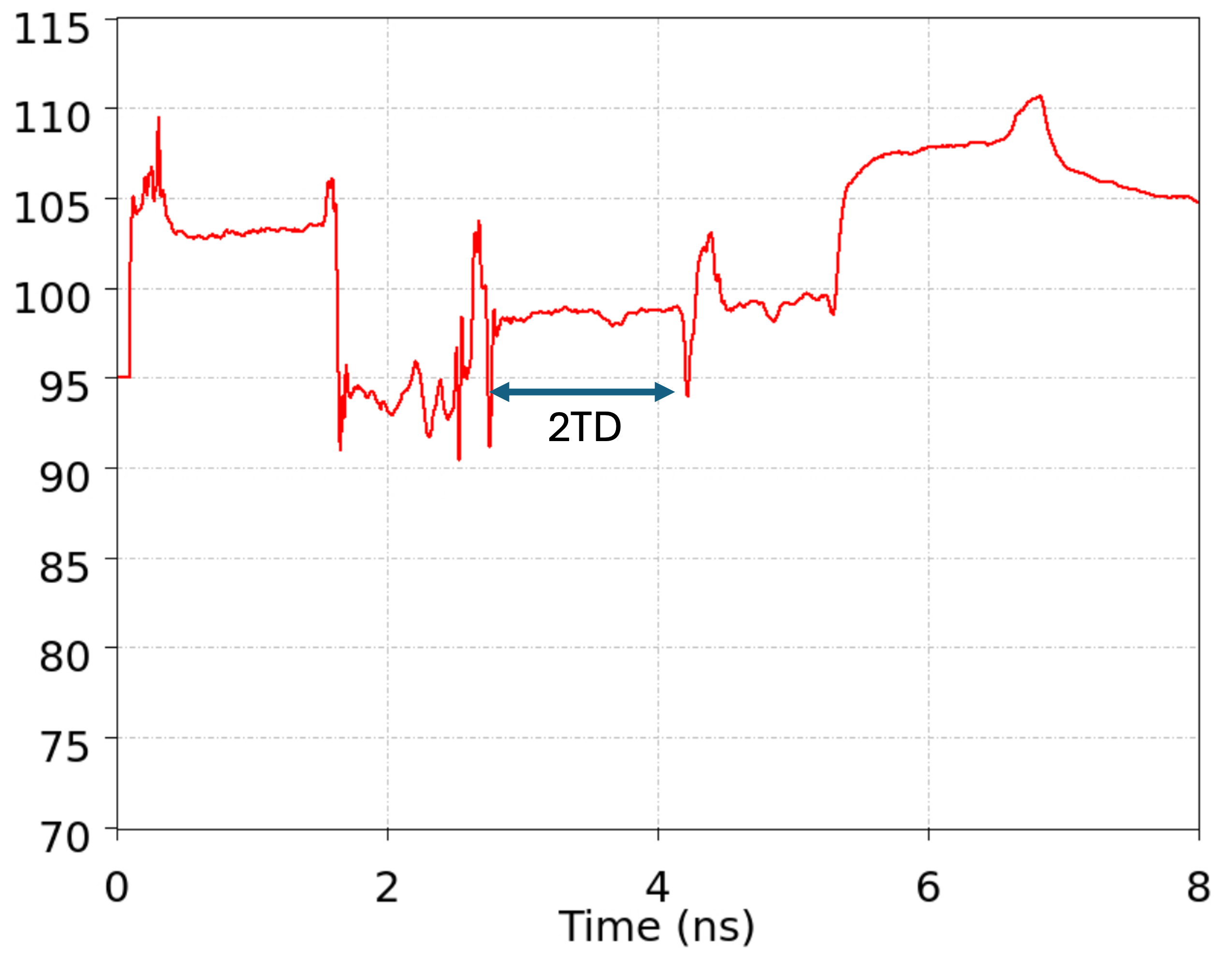

这边通过一个简单的示例来介绍如何通过TDR阻抗图计算出两两对象之间的距离:

首先,长度是波速跟时间的乘积,波在材料里面的速度跟介电常数DK有关,其中c是光速c=3 \times 10^8 m/s = 0.0118 inch/ps:

L=v×t=cDKeff−−−−−−√×t

稍作个转换会得到时间t:

t=L×DKeff−−−−−−√c

就可以得到我们要的长度L了:

L=c×tDKeff−−−−−−√

当然,如果有长度,也可以换算得到等效介电常数DKeff

DKeff=(c×tL)2

举这个案例来分析一下,两个不连续点的时间间隔是1.4ns,中间平滑的区域是传输线,Round trip delay是2TD,所以其实走完这段传输线线长大约需要700ps的时间,等效介电常数DKeff大约是3,所以稍微换算一下就可以得到长度L是4.77inch。

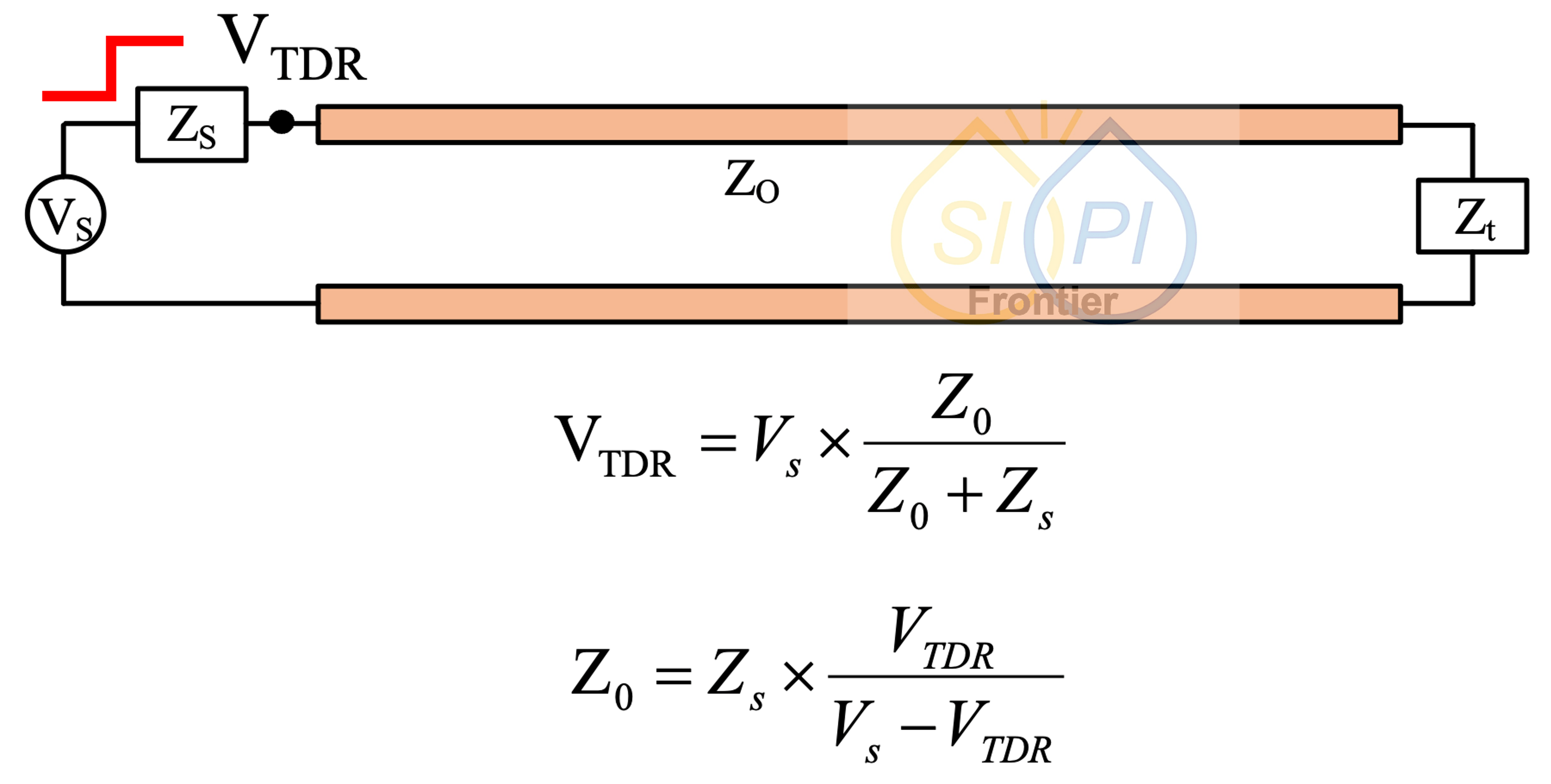

为何TDR模拟与测试时,传输线阻抗会一直往上跑?

步階波(Step Function)

简单介绍TDR后,终于来到本文主题,为何TDR测试时,容易看到传输线阻抗一路往上跑的现象?

我们先来看什么是步阶波(Step Function),这个波只有一个上升缘,是瞬时AC成分,而其它时间都是保留在low或是high level,也就是DC成分。

瞬时AC的时间才是信号会发生反射的时间点,而DC稳态则是会分压,也就是说会得到传输线的电阻。

实际的模拟结果:一探究竟为何在TDR中,传输线阻抗会爬升

我们直接通过模拟来看结果:

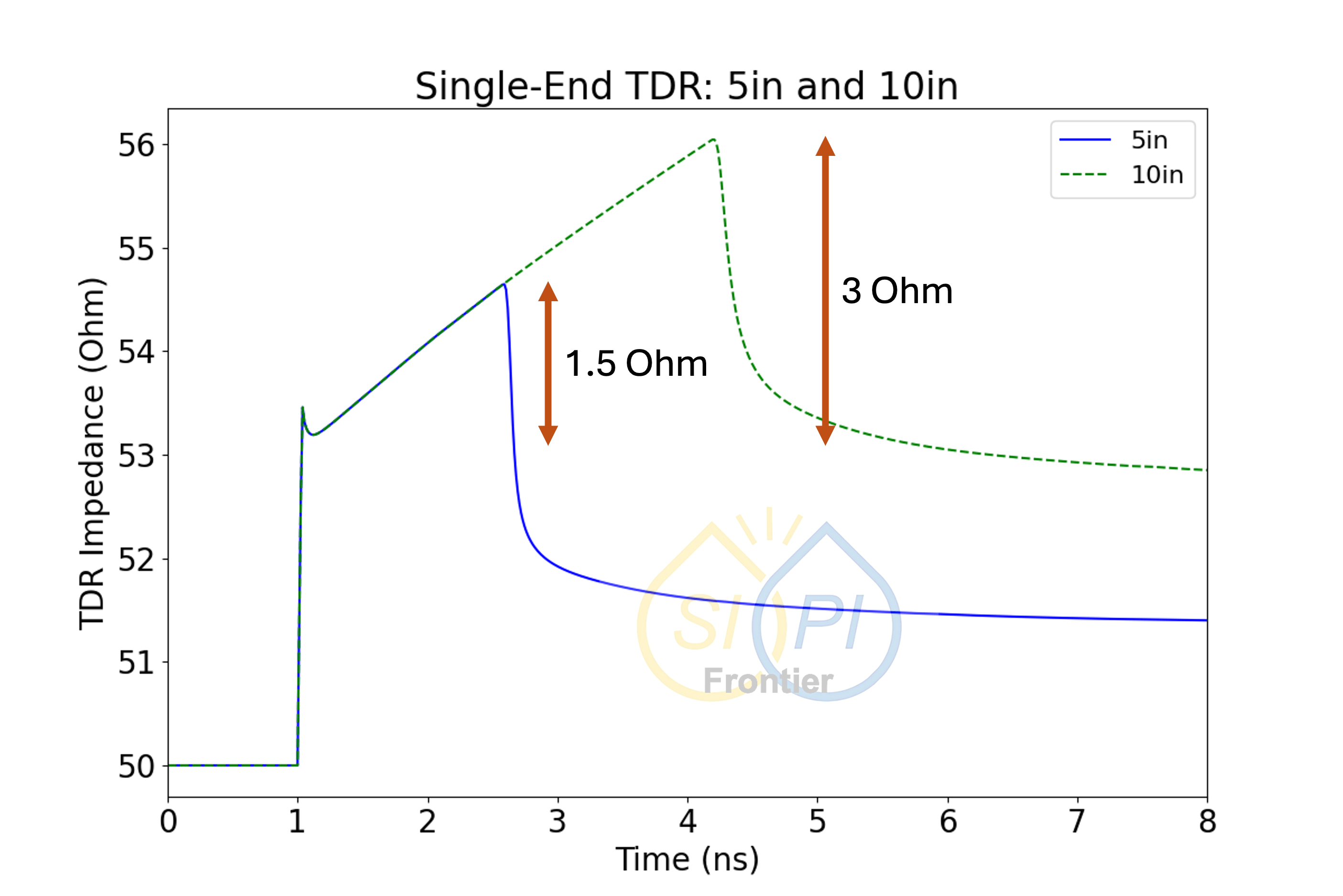

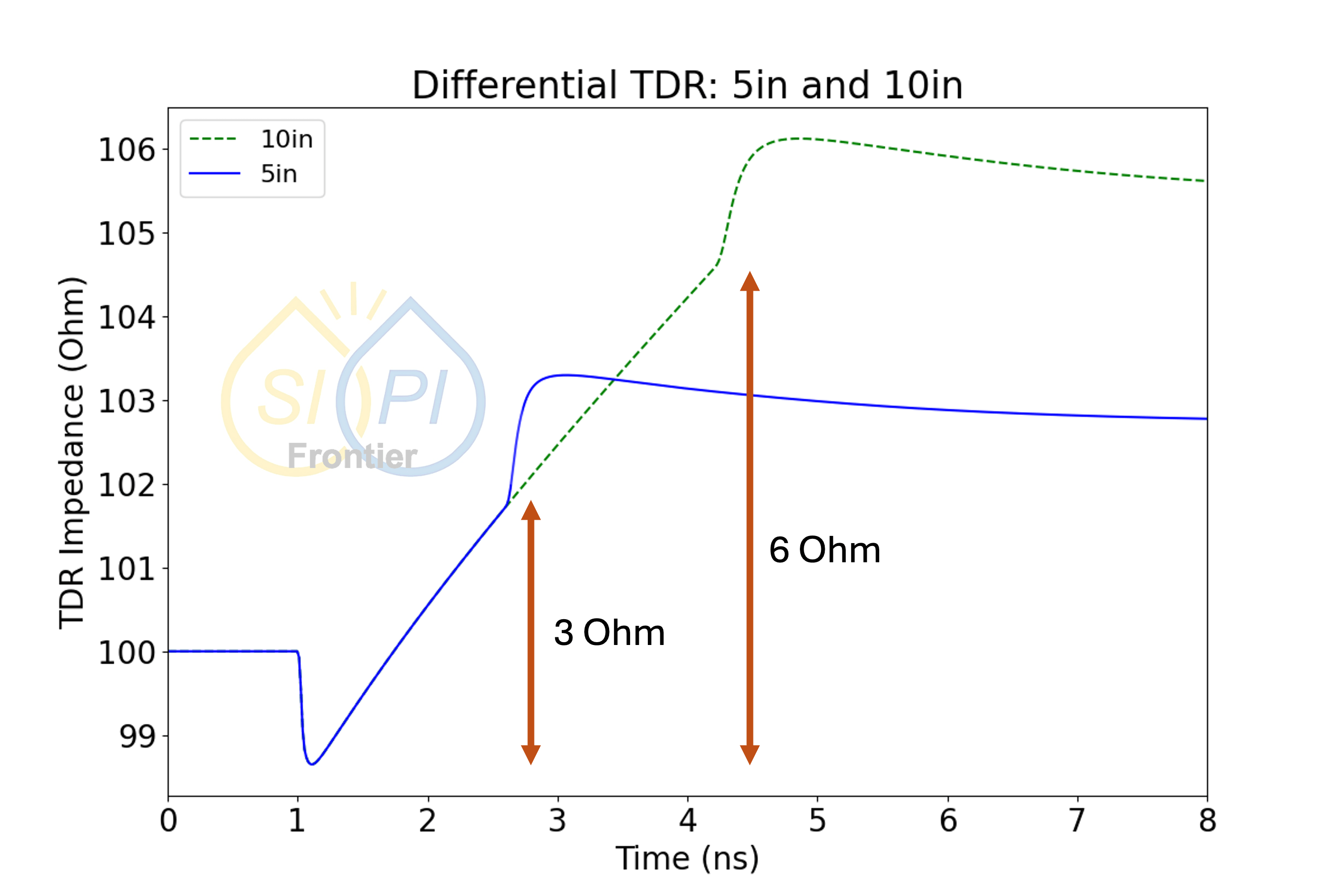

我们准备了一条理想传输线,5inch长度时,DC直流的电阻为1.5Ohm,10inch时为3Ohm。

从TDR的图来看,的确5inch的传输线会爬升1.5Ohm,而10inch传输线则会爬升3Ohm。

如果是差动对的TDR结果,会因为差动对本身是两两互相参考,所以这个电阻还会再乘两倍,5inch的线会有3Ohm的爬升,而10inch的线会有6Ohm的爬升!

以上的结果是通过电路模拟软件的W-element model萃取得到的,接下来我们透过3D软件Clarity,萃取一段真实Layout里头的传输线,这段线大约5.7inch,DC电阻大约是4Ohm左右,跟TDR的爬升幅度很类似唷!

至于在评估阻抗时,这个爬升需不需要考虑在内? 其实并不用,当您知道这个现象的缘由后,以后只需要考虑最起头的位置,那个位置显示的阻抗是95Ohm,那这条传输线的阻抗就是95Ohm啰!