PCB硬件电路设计_pcb布线设计

1.MCU最小系统电路

这些电路都会非常接近MCU,他们的可靠性决定了MCU能否正常工作。

外围电路,为了布线整齐美观,尽量避免打过多的通孔。在布局的时候走线的顺序和元器件顺序尽可能的保持一直避免走线交叉。

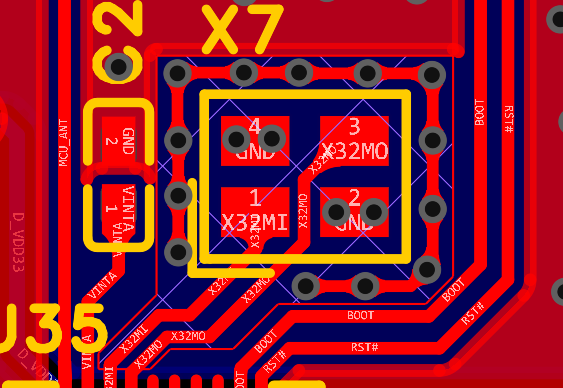

2.晶振电路布线

一般情况下我们会将晶振进行包处理,并且晶振的下方禁止走线。

3、天线布线

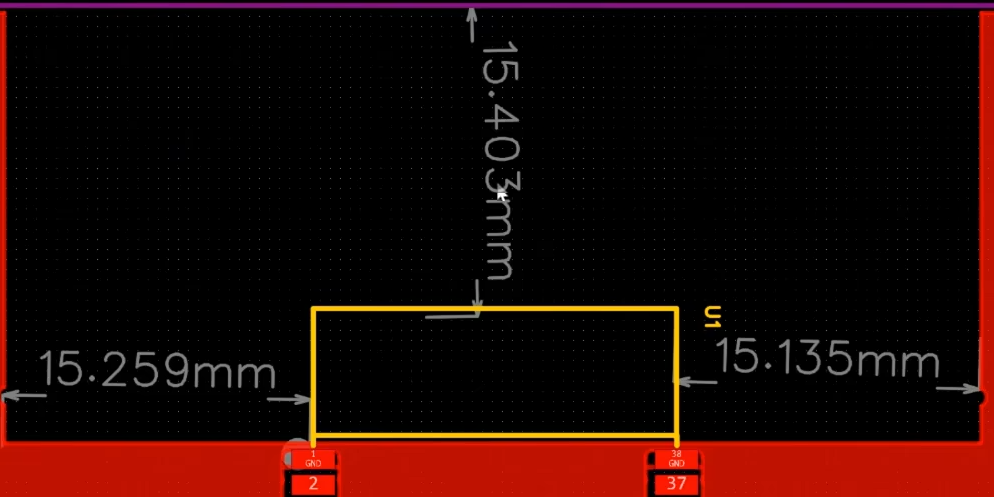

1、F类天线

例如ESP32F天线的布线,天线外围15mm以内净空。如下图所示。

因此有很多设计将天线部分放置在PCB板外,这样就不需要设计净空区。

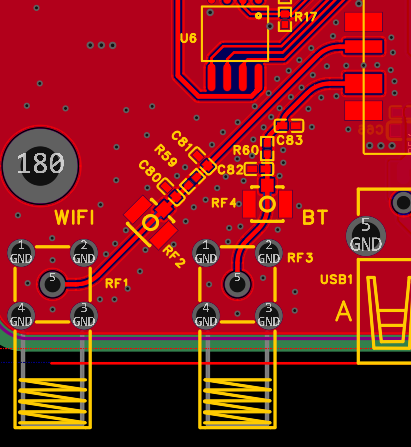

2、贴片陶瓷天线PCB设计技巧

一般情况下我们需要找到芯片厂家的数据手册,里面会有硬件设计PCB布局指导供我们参考使用。

布线技巧篇

1、在布线时MCU交叉线太多,并且PCB设计没办法规避,这时候我们就需要对原理图进行优化以便于我们布线有序。

2、有的MCU引脚之间距离很近,我们的线宽被限制,这时候MCU引脚刚出来的线我们可以画细一些,比如6mil,走个一小段之后我们可以将线画宽一些,减少走线的压降损耗。

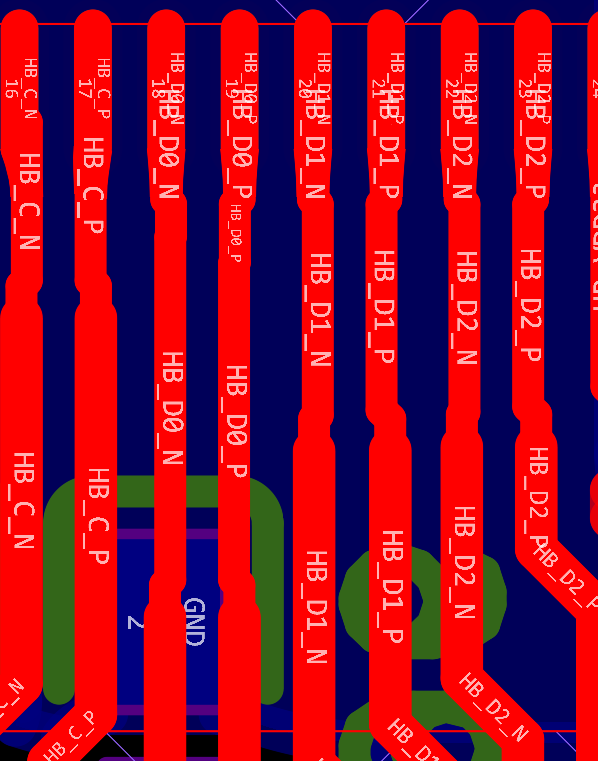

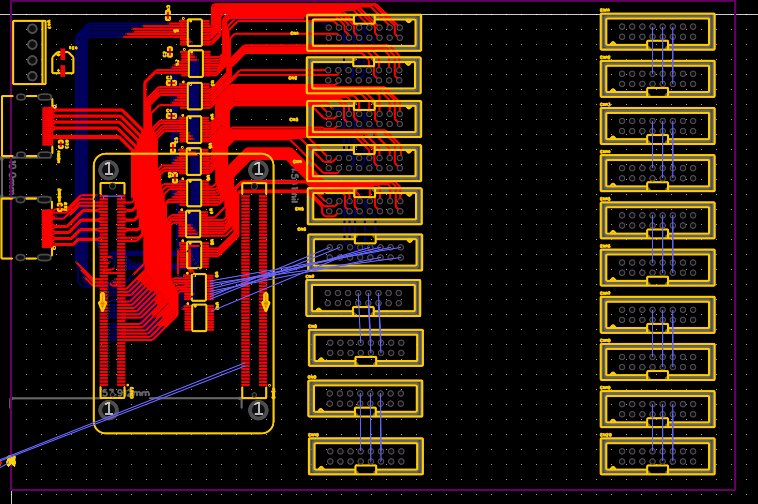

高密度布线元器件摆放技巧

1、高密度引脚尽可能的居中摆放,否则将会导致空间的浪费。

以下面这张图为例,有意左边高密度元件没有放到居中位置,导致板子上半空间没有充分利用,下半边的走线就需要更多的宽度来走线。

2.在摆放元件的时候可以观察到左边一排的控制引脚少于右边,那末我们可以将高密度元件偏上摆放,这样向下的空间就会比较大,便于走线。

25.4.28

当布线非常多的时候需要注意:

1、在布完线后不要放GND的过孔,因为如果放了过孔铺铜之后很小的区域也会有铺铜,但是这些区域极有可能与其他地是断开的。在进行DRC检查时就会包很多错误,我们就无法确定是哪个GND引脚断开了连接。

2,在生成PCB后我们禁止对元件进行翻转。会导致实际接口与PCB引脚对不上,导致板子报废。

3、在每次画板时,我们尽可能的先将原理图绘制好,绘制在画原理图会很耗费时间,也不一定会很好,在绘制的时候在已经绘制好的原理图上进行修改。

4、PCB板子圆角半径设置为3mm

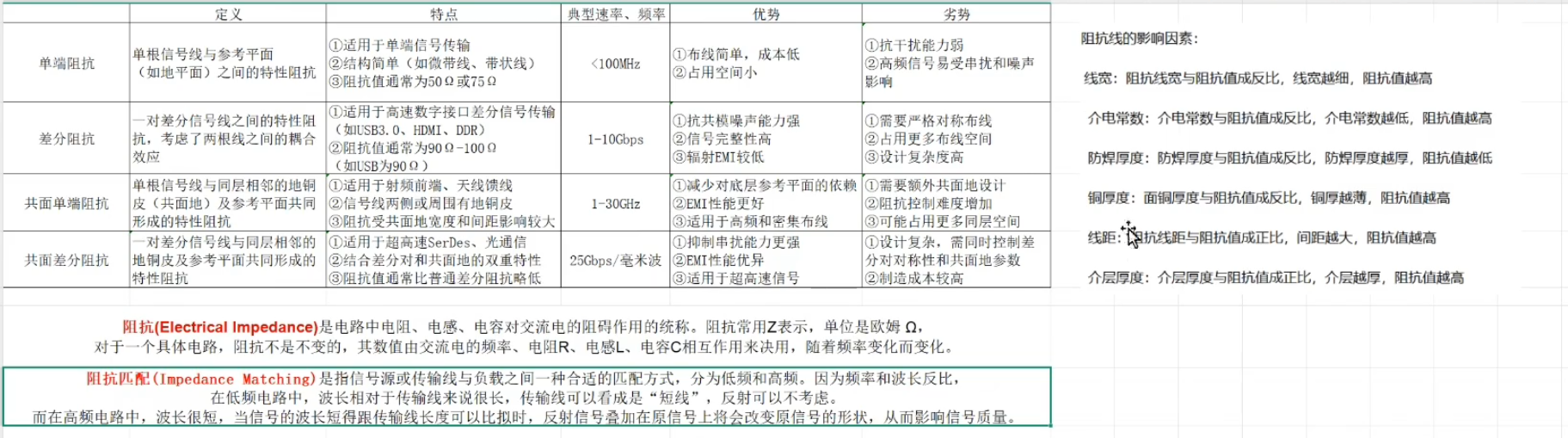

阻抗设计

单端阻抗

定义:单根信号线与参考平面(如地平面)之间的特性阻抗。

特点:适用于单端信号传输,结构简单(如微带线,带状线),阻抗值通常为50或70欧

典型速率频率:小于100MHZ。

优势:布线简单,成本低,占用空间小。

劣势:抗干扰能力弱,高频信号易受串扰和噪声影响。

差分阻抗

定义:一对差分信号线之间的特性阻抗,考虑了两根线之间的耦合效应。

特点:适用于高速数字接口差分信号传输,如(USB3.0,HDMI,DDR),阻抗值通常为90-100Ω。

HDMI阻抗一般为100偶,USB阻抗设置为90Ω。

典型速率频率:1-10GHZ

优势:抗共模噪声能力强,信号完整性高,辐射EMT较低。

劣势:需要严格的对称布线,占用更多的布线空间,设计复杂度高。

共面单端阻抗

定义:单根信号线与同层相邻的地铜皮(共面地)及参考平面共同形成的特性阻抗

特点:适用于射频前端,天线馈线。信号线两侧或周围有地铜皮。阻抗受共面地宽度和间距影响较大。

典型速率频率:1-30G

优势:减少对底层参考平面的依赖。EMI性能更好(EMI电磁干扰)。适用于高频和密集布线。

劣势:需要额外共面地设计。阻抗控制难度增加。可能占用更多层空间

共面差分阻抗

定义:一对差分信号线与同层相邻的铜皮及参考平面共同形成的特性阻抗

特点:适用于高速SerDes,光通信。结合差分对和共面地的双重特性。阻抗值通信通常比普通差分阻抗略低。

典型速率频率:25Gbps/毫米波

优势:一直串扰能力更强,EMI性能优异,适用于超高速信号。

劣势:设计复杂,须同时控制差分对对称性和共面地参数,制造成本较高。

概念:

阻抗线到铜的距离与阻抗成正比关系,其他与阻抗的关系都为反比

两层板,共面差分阻抗计算与阻抗的选择无关,下层参考一般选择第二层。线距:两个差分线的线边距。阻抗线到铜的距离:线边到地铜皮之间的距离

阻抗计算与技巧

根据我们布线和板子的层数,确定我们布线的类型。通过调节线距和阻抗线到铜的距离使得计算出来的线宽满足我们的设计需要。在根据线宽,线距,线到铜距设定规则,然后进行约束区限制,使得这部分区域符合我们的设计要求。

3W原则

3W原则是指多个高速信号线长距离走线的时候,其间距应该遵循3W原则,例如时钟线,差分线,视频、音频信号线,复位信号线及其他系统关键电路需要遵循3W原则,而并不是板上所有的布线都要强制符合3W原则。