NVLink、UALink 崛起,PCIe Gen6 如何用 PAM4 迎战未来?

现在数字经济发展地相当快速,像Cloud、现在火红的AI、大数据这些新技术都需要在数据中心里运行更多运算,伴随而来的是更快的数据传输速度的需求。 在数据中心,有很多条数据传输路径,举例 :

- Server 和Storage之间(通过PCIe)

- CPU和各种适配器之间(通过PCIe)

- GPU跟GPU组成的Cluster (透过NVLink或Ethernet)

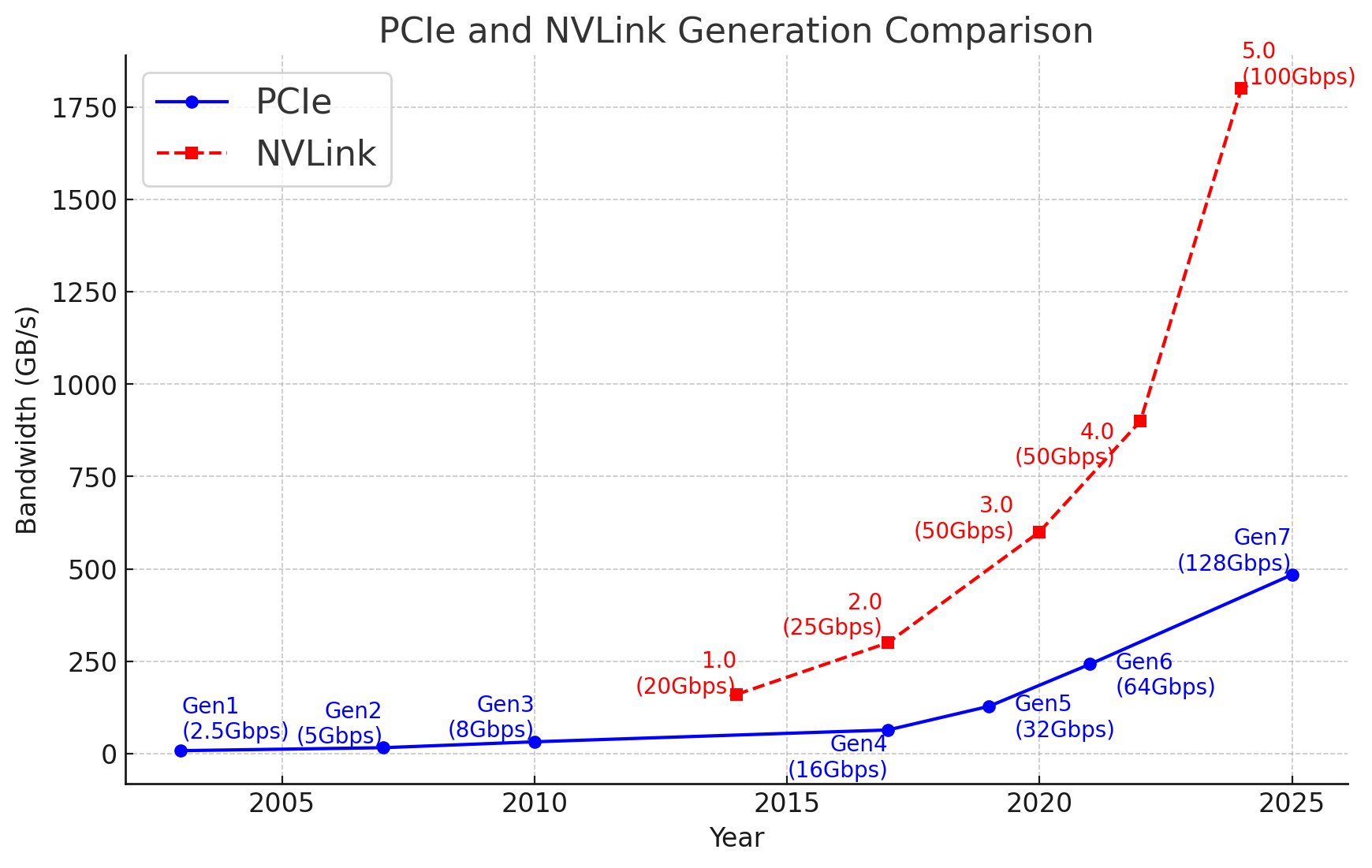

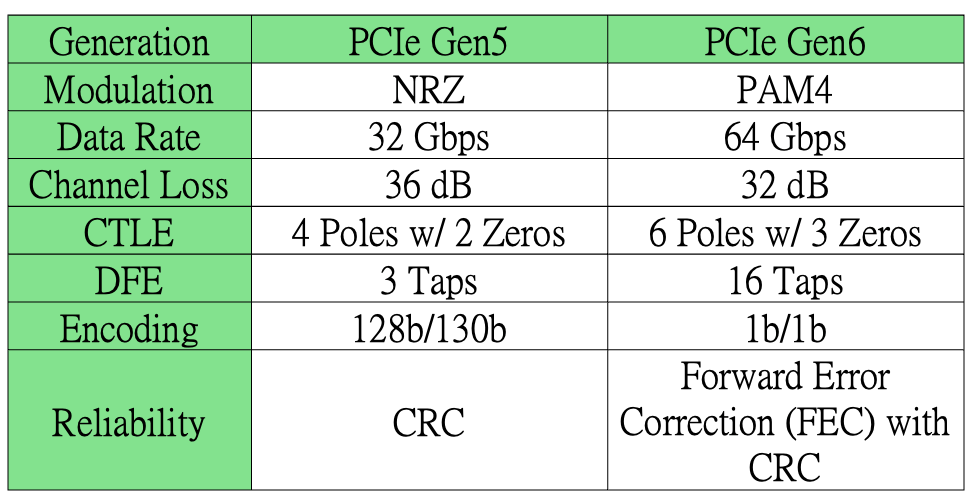

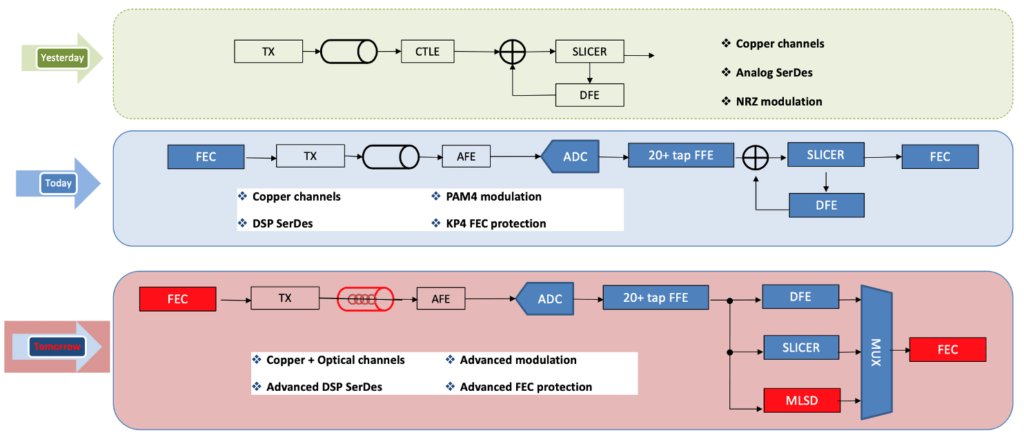

相当多样的数据传输拓朴不停交换大量数据,以应付即时运算和庞大的数据读写需求。 所以,硬件接口技术也必须不断升级,否则整个系统就会被数据传输带宽给卡住。 在传统服务器领域,一直都是PCIe当作主要高速传输媒介,靠着将每个Lane的Data Rate提高,进而提升整体带宽。 但到了PCIe Gen6这一关,单靠传统的NRZ编码技术已经遇到相当大的瓶颈。

P.S. 由于PCIe的演进太慢,带宽太差,因此nVIDIA自行研发NVLink(已经要迈向200G-PAM4)将自己的芯片构建成的系统达到另一个层次,这其实是Ethernet网络的领域,咱们再另外说明! 这也是为什么会有UALink的缘故!

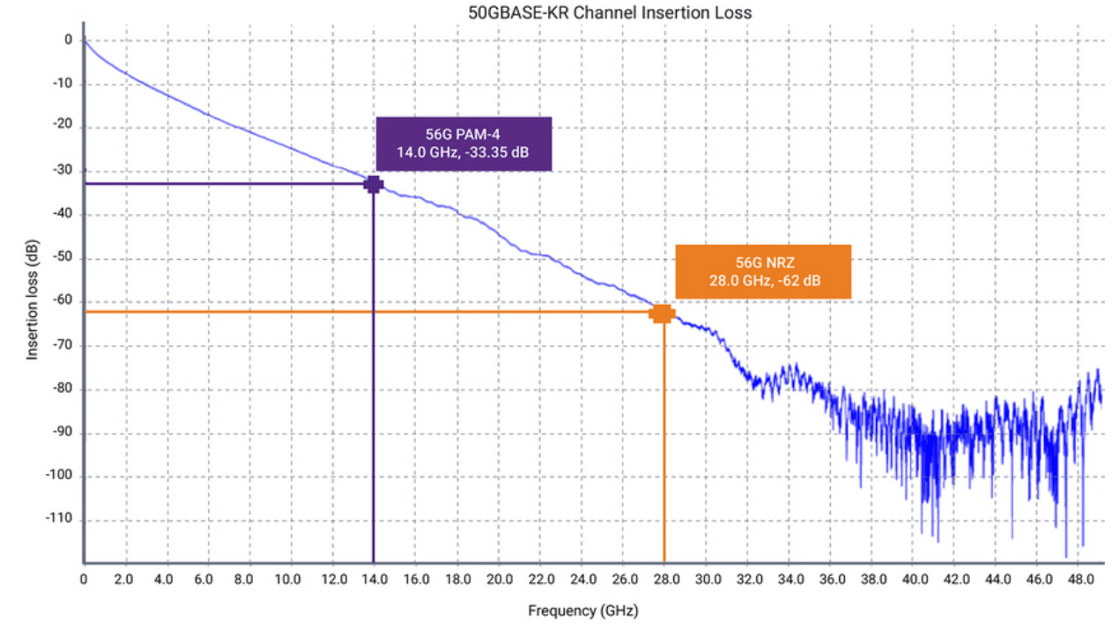

为什么说Gen6会有瓶颈? 主要原因在于SI的综合考量。 Gen6的Data Rate是64Gbps,相较Gen5的32Gbps多了一倍,如果利用NRZ编码技术,最高的Clock频率高达32GHz(或者可以说Nyquist Frequency),这使得我们在关注的损耗带宽不好实现。 如图片说明,56Gbps-NRZ的通道损耗在28GHz高达62dB,现今等化器(Equalizer, EQ)技术可无法到达这一水平。 而PAM4的讯号调变方式将带宽再多降低一倍至14GHz,相同通道的损耗可以变小为33dB,对EQ来讲相当友善!

为什么 PCIe Gen6 使用 PAM4 ?

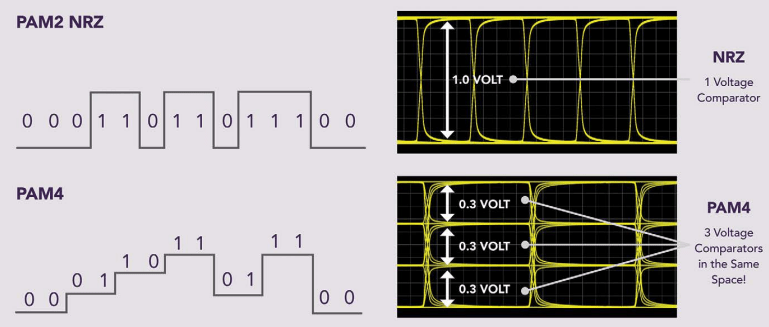

传统通道调变技术是NRZ (或称作PAM2),只有两个电压阶层,每个符号(Symbol)仅能承载 1 bit 资讯,若硬要单靠NRZ再将符号速率倍增,就必须在更高的频段运作,带来严重的高频损耗,同时需要在材料和走线技术上付出极高成本才能维持良好的讯号质量。

PAM4技术正好满足了这个「有限带宽中实现高数据密度」的需求。 PAM4 在同样的数据传输速度下,把信号幅度划分成四个等级,因而在一个符号间隔中能传递 2 bit 的信息。 换句话说,相同速度下PAM4可以传递两倍于NRZ的数据,有效带宽自然可以再往下降。

除了在速率与带宽之间取得较好的平衡,PAM4 另一个优势在于整个高速领域已经累积了相当多的应用经验。 在Ethernet领域,56G和112G SerDes已采用PAM4调变,所以芯片IP、量测设备和高速布线技术已相当成熟,也让业界对PAM4的噪声模型、EQ、FFE/DFE都有了深厚的研究。 所以PCIe采用PAM4,也就能承接这些既有的技术成果与生态系统,减少从零开始摸索的风险与成本。

PCIe Gen6 PCB Material Selection from SI View

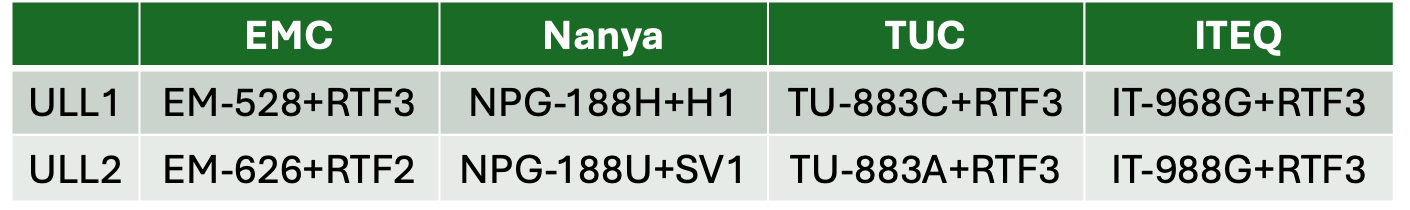

有别于PCIe Gen5的36dB,PCIe Gen6的Channel loss budget为32dB。 Intel的文件里有提到,从Gen5的Birch Stream升级到Gen6的Oak Stream会需要将CCL材料的等级从ULL1(0.96dB/inch)提升到ULL2(0.85dB/inch),从台湾的CCL供应链来看,台光电推出高性价比的EM626抢攻市场,台曜与联茂各有相关解决方案。 其中南亚较晚切入中高阶领域,刚进来就推出极高性价比的NPG-188U,据说已经有许多ODM导入使用中。

PAM4’s Challenge

然而事情总是一体两面,PAM4也是带来相当多的挑战:

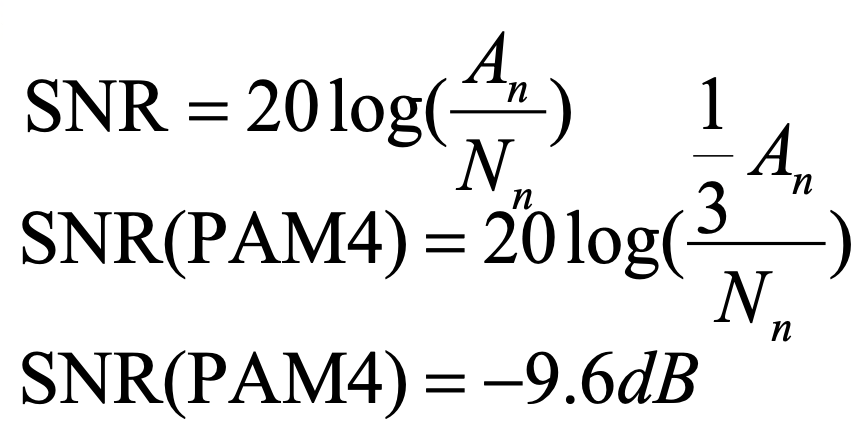

- 较差的SNR(Signal-to-Noise Ratio): 由于原先的振幅范围内要多塞进两个电压准位,所以有别于NRZ眼图的一颗眼睛,PAM4眼睛会有三颗,振幅缩小1/3,也就是说天生的SNR就比NRZ调变少了9.6dB。

- 抗噪声能力差:由于天生少了9.6dB的SNR,使其对于噪声较为敏感,一般对于NRZ的Power-Sum Crosstalk要求是-30dB,而PAM4我们会尽量要求在-45dB。

- EQ设计更复杂:由于天生较低的SNR,导致Receiver需要用更强的EQ补偿信号,设计者与测试单位需要更多地理解这些EQ的任务。

- FEC(Forward Error Correction):可以针对误码进行侦错并纠错,不过系统延迟会上升。

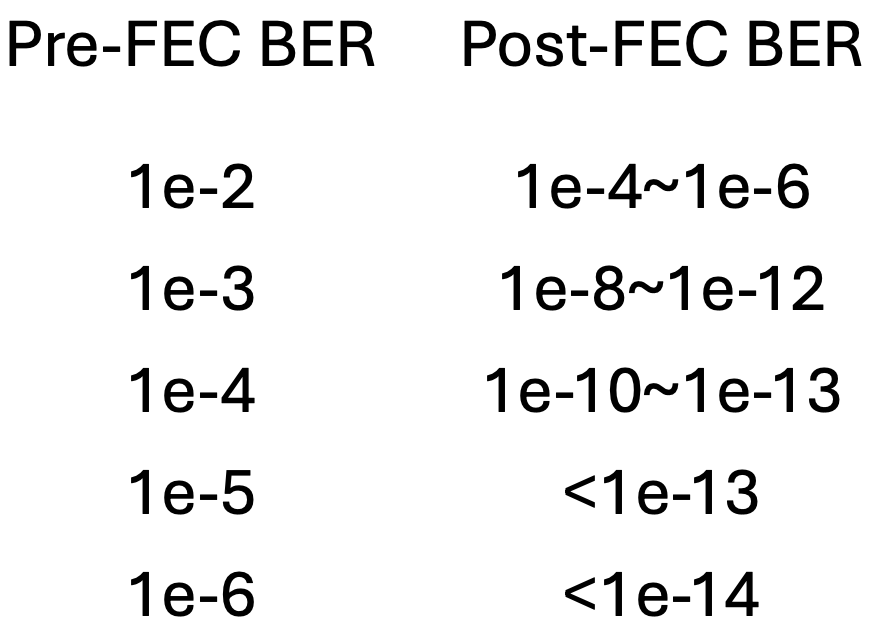

- NRZ的BER要求是小于1e-12,但是PAM4的Pre-FEC BER(或称作Raw BER)则是1e-5左右,透过FEC的纠错可以将Post-FEC BER降低至1e-12以下。

- 较大的功耗:由于引入比较多的EQ,且使用了FEC,这些新导入的技术会大大地提升整个系统功耗,使得电源完整性与PCB板温的议题浮上台面。 (P.S.这也是为什么Linear Pluggable Optics, LPO被提出来的主要原因)

- 测试设备升级:PAM4不再是一个单一眼图,而是三个「眼」需要同时观测与评估,量测示波器与 BERT必须支持更高带宽与更细腻的分析功能。

PAM4的确是可以将设计的有效带宽降低,在PCB材料的选择上保持更多弹性,不过设计者得面临更高层次的 SI/PI考量、电路设计复杂度,以及测试验证的高门槛。 在台湾,由于设计Ethernet的人跟PCIe的人比较不会overlap,所以目前设计PCIe的人初期可能会比较辛苦,但将设计面向放宽,多留些Margin,一定可以轻松征服PAM4!