利用Python生成Xilinx FPGA ROM IP核 .coe初始化文件

以下是一个 Python 脚本,用于生成 Xilinx IP ROM 的.coe 格式初始化文件,假设ROM 深度为 1024,数据位宽为 32bit,使用随机的 32 位无符号数进行初始化:

import random# 定义ROM的深度和数据位宽

rom_depth = 1024

data_width = 32# 生成随机的32位无符号数

random_numbers = [random.randint(0, 2**data_width - 1) for _ in range(rom_depth)]# 打开文件以写入模式

try:with open('rom_init.coe', 'w') as file:# 写入文件头file.write('memory_initialization_radix=16;\n')file.write('memory_initialization_vector=\n')# 写入随机数据for i, num in enumerate(random_numbers):if i < rom_depth - 1:file.write(f'{num:08x},\n')else:file.write(f'{num:08x};')print("COE文件已成功生成:rom_init.coe")

except Exception as e:print(f"写入文件时出现错误:{e}")

这个脚本完成以下操作:

- 导入random模块,用于生成随机数。

- 定义 ROM 的深度和数据位宽。

- 生成指定数量的随机 32 位无符号数。

- 打开一个名为rom_init.coe的文件,并以写入模式写入数据。

- 写入文件头,指定数据的基数为 16 进制。

- 依次写入随机数据,每行一个数据,最后一个数据以分号结尾。

- 捕获并处理可能出现的文件写入错误。

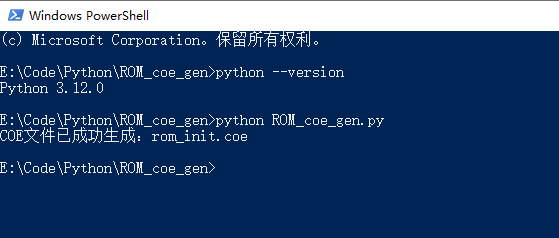

运行结果:

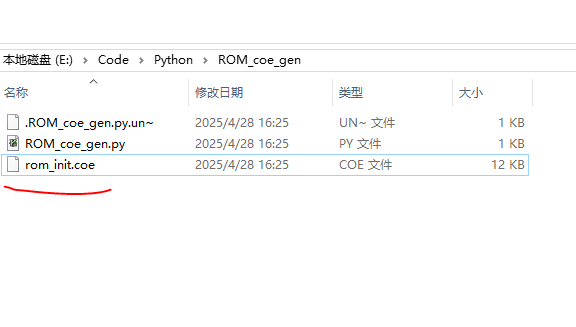

初始化文件rom_init.coe已经生成

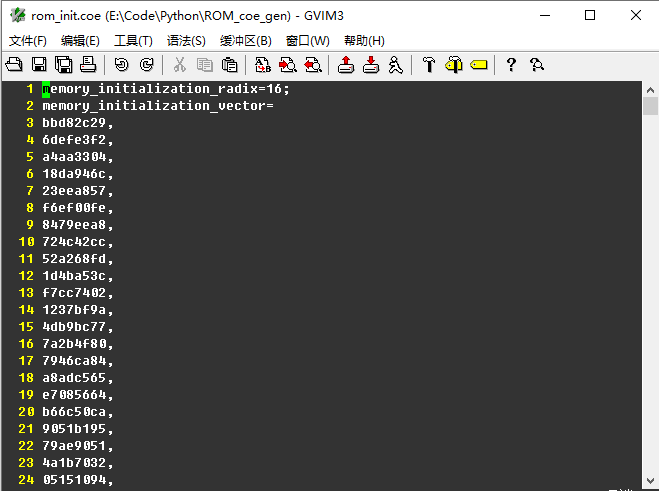

rom_init.coe文件内容: