06-stm32时钟体系

一、时钟体系

1、概念

1.时钟信号:是一种周期性的电信号,例如为方波,正弦波,余弦波等各种波形,用于同步数字电路中的各种操作,它控制着数据的传输以及电路状态的变化。

2、时钟系统在 STM32 的系统中扮演着关键的角色,它的稳定性和精度对整个系统的性能影响很大。STM32 的时钟系统由外部晶振、PLL(锁相环)和内部 RC 振荡器组成。

3、时钟系统的作用:

- 为处理器提供准确的时钟信号,保证处理器、总线和外设的正确工作。

- 通过 PLL 的倍频功能,产生多种频率的时钟信号,满足不同外设的时钟需求。

- 通过时钟系统提供的时钟分频器、预分频器等功能,进一步调整时钟频率,以适应不同的应用场景。

4、时钟源分类

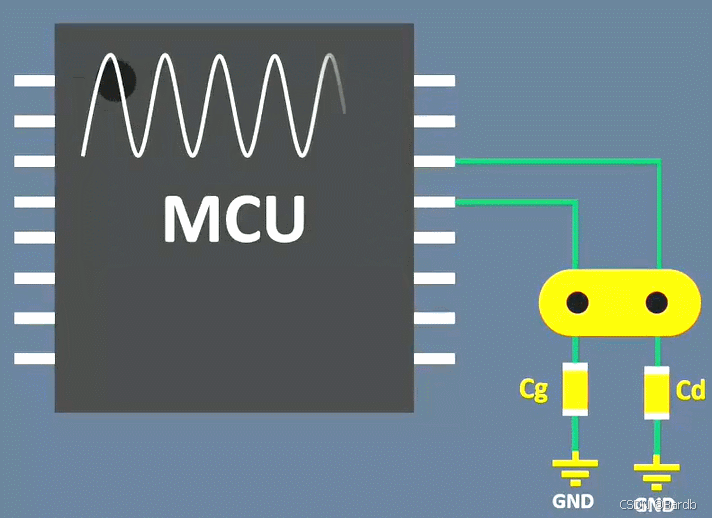

1.晶振(Crystal Oscillator):电路设计时,它在在芯片外部,最常见的时钟源之一,通过石英晶体的机械振动来产生非常稳定和精确的频率。它可以产生方波,类似于人体的心脏。提供脉搏的,而它是给CPU提供波形。

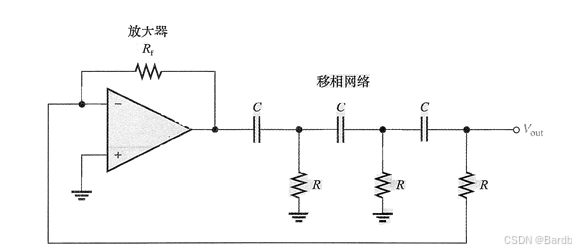

2. RC振荡器

3.PLL:相位锁定环可以用来调整时钟信号的频率和相位,或者从一个较低频率的时钟信号生成多个较高频率的时钟信号。

2、STM32主要的时钟源

1、内部RC振荡器 (HSI,High Speed Internal)即HSI

- 描述: HSI是一个出厂预校准的内部RC振荡器,在STM32F407中默认频率为16 MHz。

- 用途: 适用于开发初期调试、低功耗应用或者不需要高精度时钟的应用。

- 特点: 不需要外部晶体,成本较低,启动速度快。

![]()

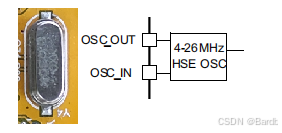

2、 外部高速时钟 (HSE,High Speed External):

- 描述: HSE是通过外部晶体或陶瓷谐振器提供的时钟源,其频率取决于所选的晶体。

- 用途: 适用于需要高精度和稳定性的应用,如通信接口、实时操作系统等。

- 特点: 需要外部元件,启动速度较慢,但精度较高。

3、内部低速振荡器 (LSI,Low Speed Internal)

- 描述: LSI是一个内部RC振荡器,通常用于RTC、备份域时钟、内部独立看门狗。

- 用途: 适用于低功耗模式下维持时间或计数。

- 特点: 不需要外部元件,但精度较差。

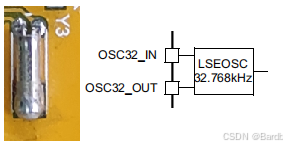

4、外部低速时钟 (LSE,Low Speed External):

- 描述: LSE是通过外部晶体或谐振器提供的低速时钟源,通常用于RTC或备份域时钟。

- 用途: 适用于需要精确计时的应用,如实时时钟RTC。

- 特点: 需要外部元件,但提供较高的精度。

3、时钟频率单位

1、时钟频率单位:GHZ MHZ KHZ HZ

1HZ即1秒产生一个方波、 正弦波等波形。

单位换算:1GHZ = 1000MHZ = 1000 000KHZ = 1000 000 000HZ

频率越高,CPU/MCU的性能越强.(其他条件同等的情况下)

4、STM32微控制器的时钟源应用场景

🔸低功耗应用:

- 使用HSI作为主要时钟源,因为它不需要外部晶体并且启动迅速。

- 在深度睡眠模式下,可以仅保留LSI来维护RTC计时。

🔸实时操作系统 (RTOS):

- 使用HSE作为主要时钟源,因为它提供更准确的时间基准。

- 可以配置PLL来获得更高的系统时钟频率,以满足RTOS任务调度的需求。

🔸高速数据采集:

- 使用HSE结合PLL来达到最高的系统时钟频率(例如168 MHz)。

- 这样的配置可以提高ADC、DAC以及其他高速外设的采样率。

🔸无线通信接口:

- 对于需要精确时钟同步的接口(如USB OTG FS/HS、SDIO等),通常需要使用PLL输出的时钟。

- HSE通常是这类应用的首选时钟源,因为它的稳定性和精度更好。

🔸实时时钟 RTC:

- RTC通常由LSE驱动,以确保即使在主电源关闭的情况下也能保持时间准确。

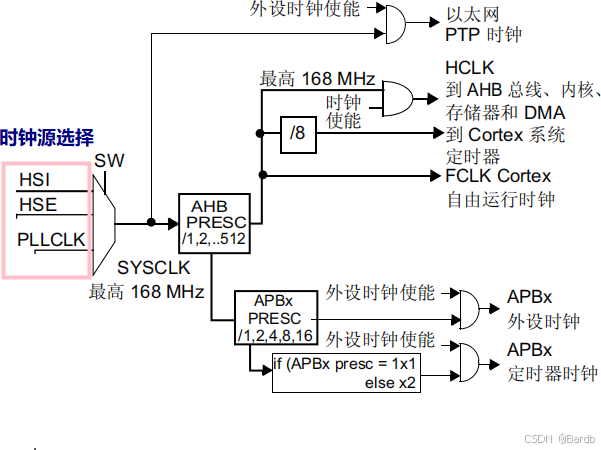

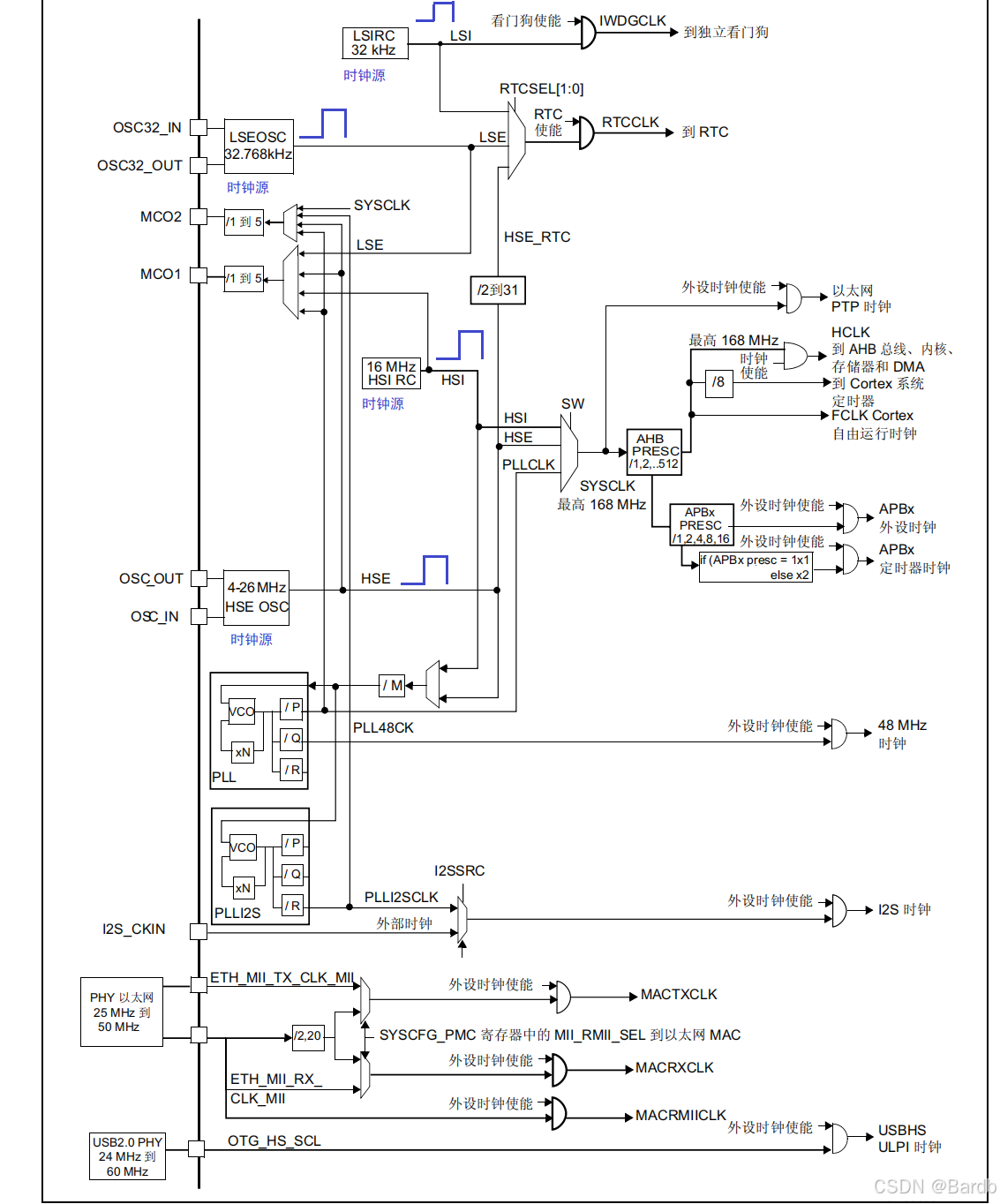

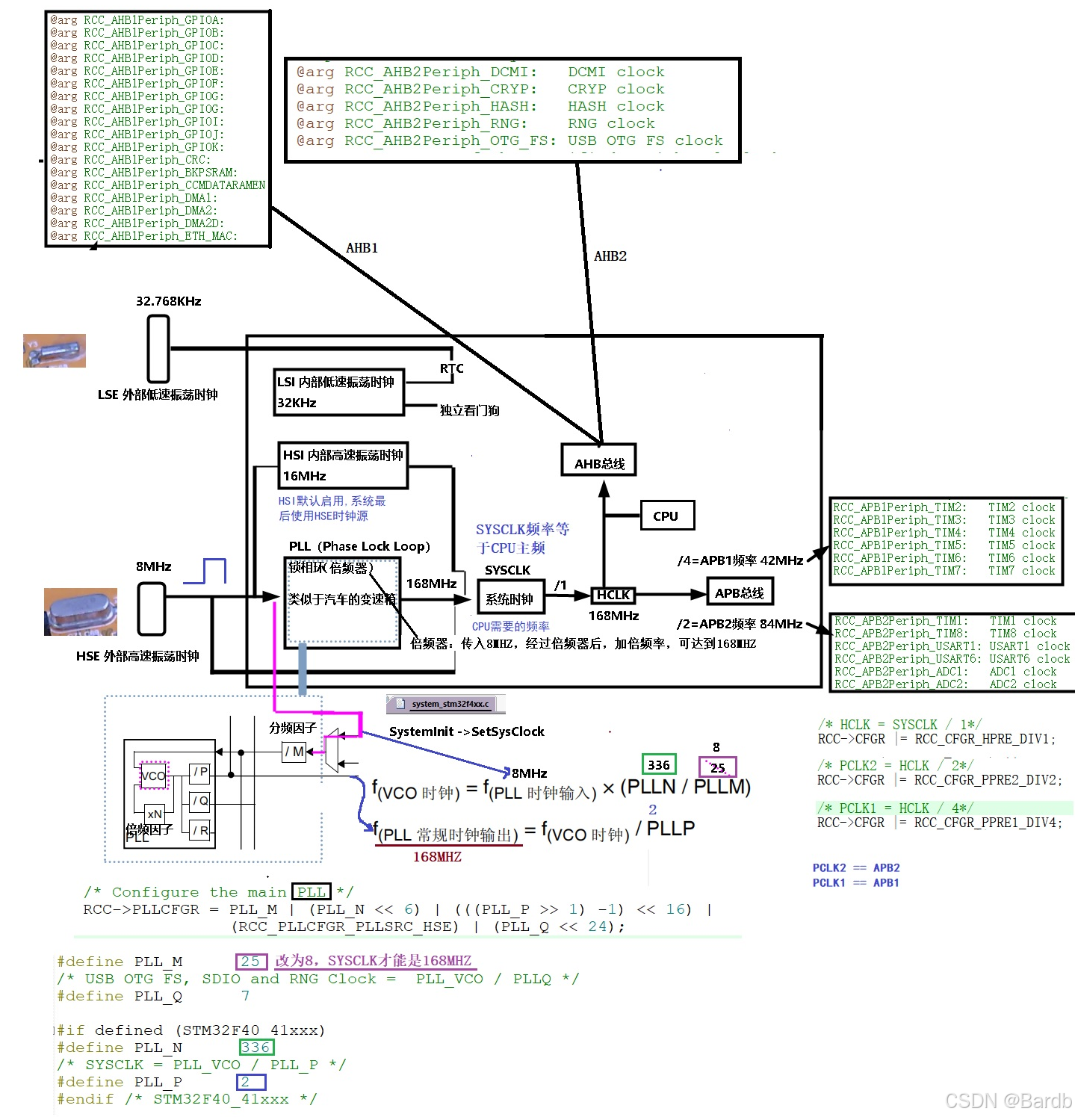

二、时钟树结构

1、结构如下:

STM32F407的时钟树结构如下:

HSI / HSE Oscillator

- HSI和HSE振荡器为系统提供了主时钟源。

- HSI默认启用,而HSE需要通过软件手动启用。

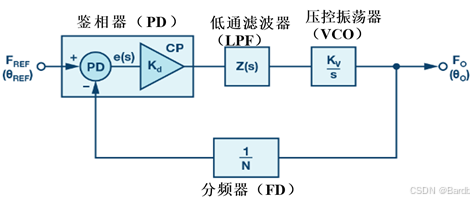

PLL (Phase Locked Loop)

- PLL可以从HSE、HSI作为输入源,输出频率可以配置。

- STM32F407的PLL可以为系统时钟提供高达168MHz的频率。

AHB Prescaler

- AHB预分频器用于调整AHB总线时钟频率,它可以分频系统时钟(SYSCLK)。

APB1 Prescaler

- APB1预分频器用于调整APB1总线时钟频率,它可以进一步分频AHB总线时钟。

APB2 Prescaler

- APB2预分频器用于调整APB2总线时钟频率,它可以进一步分频AHB总线时钟。

LSI / LSE Oscillator

- LSI和LSE振荡器用于RTC和备份域。

2、时钟树框图

简图:

📣总结:

stm32对每个外设的时钟都设置了开关,让用户可以精确地控制,关闭不需要的设备,达到节省供电的目的。如果不用的就完全关闭,尽可能降低芯片功耗。

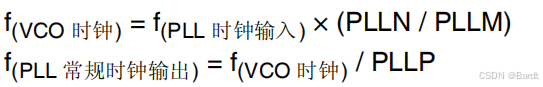

3、PLL锁相环

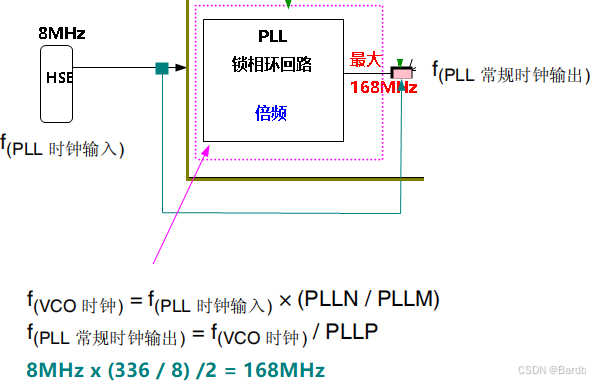

stm32f407配置PLL参数的公式

💡注:不同的芯片,倍频(频率翻倍)公式是不一样的,需要查询芯片手册!

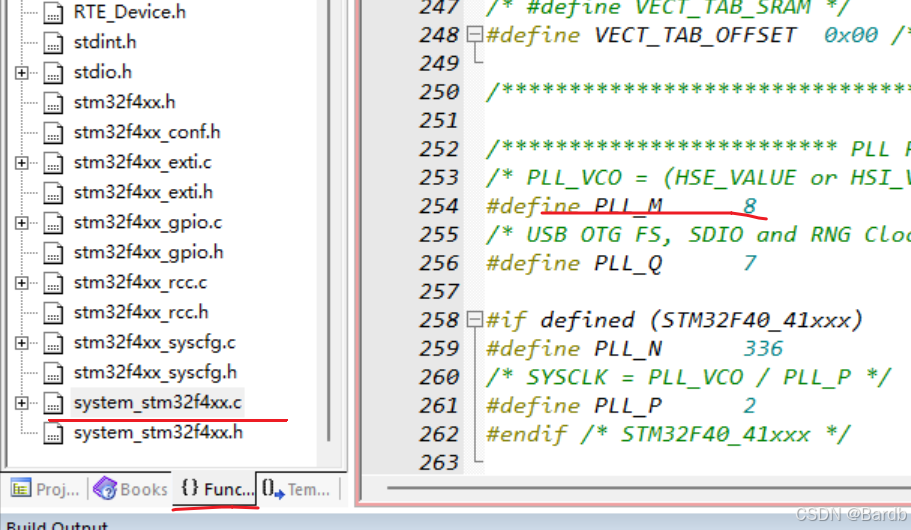

三、SystemInit系统初始化函数

1、 system_stm32f4xx.c文件有以下倍频(PLL_N)与分频(PLL_M、PLL_P)因子:

由于官方的代码是使用外部高速晶振25MHz,GEC-M4开发板是使用外部高速晶振8MHz,所以PLL的倍频因子要进行修改,只修改PLL_M为8。

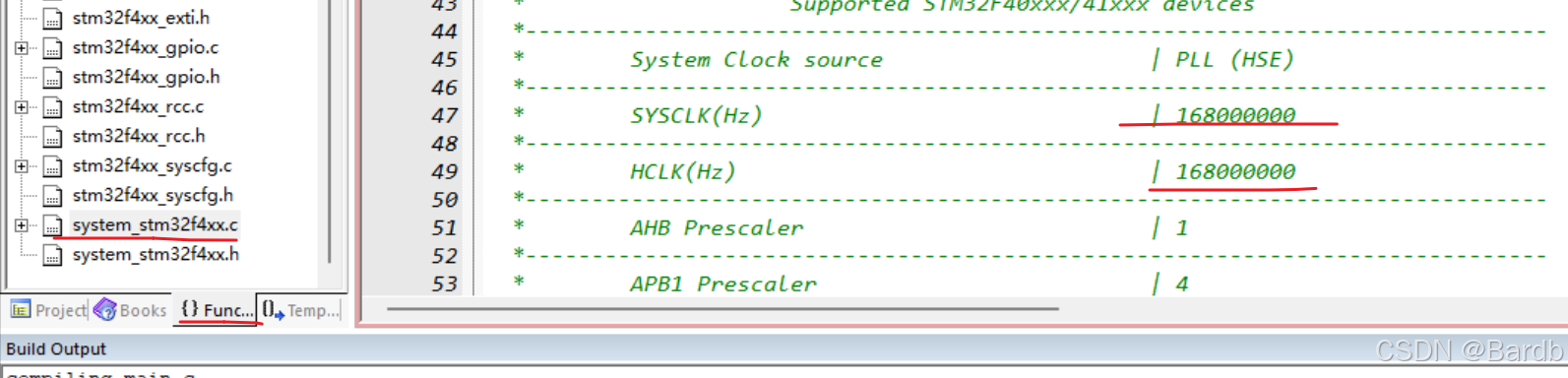

2.阅读system_stm32f4xx.c文件的头部注释,若需要配置SYSCLK为168MHz,按照以下参数配置。

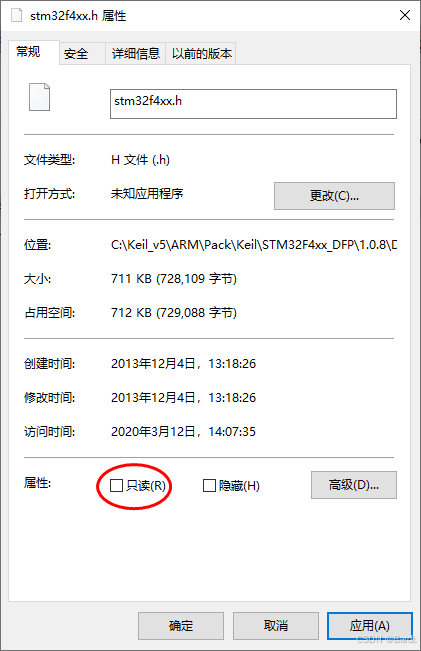

3、设置外部高速振荡时钟频率,须去掉stm32f4xx.h的只读属性。

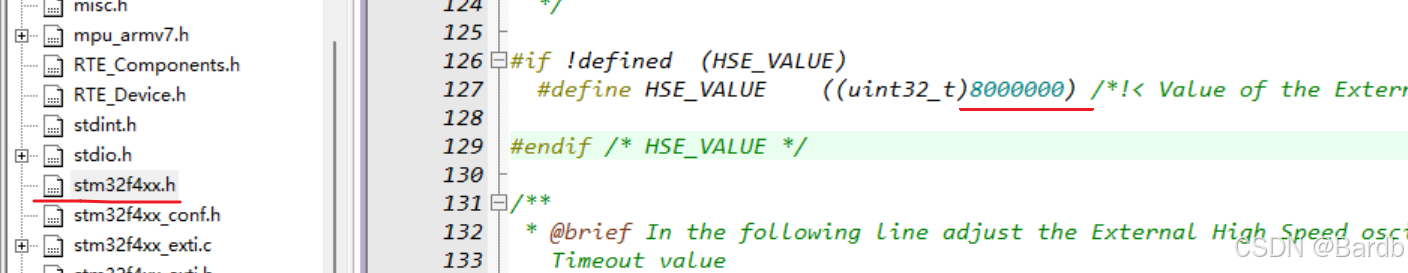

4、接着修改stm32f4xx.h以下内容,行127将外部晶振频率值修改为8MHz。

5、最后按照PLL的运算公式,最终得到输出频率为168MHz。

四、时钟源

在特殊的应用场景,为了达到最高的能效比,没有必要使用到PLL,可将HSE、HSI作为系统时钟源。例如,在智能手表锁屏的情况下,如果使用PLL配置过后输出的频率会造成过多的功耗,降低自身的续航能力;同时要维持计步与测量心率功能。因此,PLL在锁屏下的应用场景并不合适,在保证功能实现的前提下,尽可能降低功耗,可以切换频率更低的时钟源提供给系统时钟。